─XÖCĮė┐┌BCI(Brain Computer Interface)╩Ūę╗ĘNą┬ĘfĄ─╚╦ÖCĮė┐┌ĘĮ╩ĮĪŻ╦³Ą─Č©┴x╩ŪŻ║▓╗ę└┘ćė┌─XĄ─š²│Ż▌ö│÷═©┬Ę(═Ōų▄╔±ĮøŽĄĮy╝░╝Ī╚ŌĮM┐Ś)Ą──X-ÖC(ėŗ╦ŃÖC╗“Ųõ╦¹čbų├)═©ėŹŽĄĮy[1]ĪŻę║Š¦├µ░Õū▀ä▌ę¬īŹ¼F─XÖCĮė┐┌Ż¼▒žĒÜėąę╗ĘN─▄Ę┤ė│╚╦─X▓╗═¼ĀŅæBĄ─ą┼╠¢Ż¼▓óŪę─▄ē“īŹĢr╗“Č╠Ģrī”▀@ĘNą┼╠¢▀Mąą╠ß╚Ī║═ĘųŅÉ[2]ĪŻ╦▓æBęĢėXšT░lļŖ╬╗┼c┤╠╝żų«ķgŠ▀ėąć└Ė±Ą─µiĢr═¼▓ĮĻPŽĄŻ¼─▄▒╚▌^£╩┤_ĄžÖz£yę║Š¦├µ░Õū▀ä▌,Č°Ūę╦³╦∙ąĶĄ─ęĢėX┤╠╝żŅl┬╩▒╚▌^Ą═Ż¼▓╗╚▌ęūę²ŲęĢėXŲŻä┌ĪŻę“┤╦▒ŠčąŠ┐▓╔ė├╦▓æBęĢėXšT░lļŖ╬╗üĒīŹ¼F─XÖCĮė┐┌ĪŻ

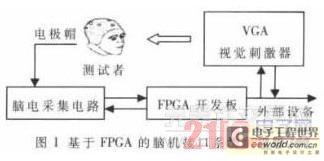

─XÖCĮė┐┌ŽĄĮy╩Ūė╔╚╦║═ÖCŲ„śŗ│╔Ą─ķ]ŁhŽĄĮy[3]ĪŻ│²╚╦▒Š╔Ē═Ō, ─XÖCĮė┐┌ŽĄĮy░³└©Ż║ą┼╠¢▓╔╝»Īóą┼╠¢╠Ä└ĒĪó═Ō▓┐įOéõ╝░┐žųŲ▓┐ĘųĪŻ▒Š╬─Ą─ĘĮ░Ė▓╔ė├FPGA╚Ī┤·ėŗ╦ŃÖCŻ¼ū„×ķ─XÖCĮė┐┌Ą─┐žųŲ║═ą┼Žó╠Ä└ĒŲ„ĪŻų„ę¬░³└©─XļŖ▓╔╝»ļŖ┬ĘĪó╗∙ė┌FPGAĄ─VGAęĢėX┤╠╝żŲ„║═FPGAķ_░l░Õ╚²▓┐ĘųŻ¼╚ńłD1╦∙╩ŠĪŻ

ļŖśO├▒║═─XļŖ▓╔╝»ļŖ┬ĘĮM│╔┴╦─XļŖą┼╠¢▓╔╝»▓┐ĘųĪŻę║Š¦├µ░Õū▀ä▌VGAęĢėX┤╠╝żŲ„ī┘ė┌═Ō▓┐įOéõ╝░┐žųŲ▓┐ĘųĪŻFPGAķ_░l░Õ╩Ūš¹éĆŽĄĮyĄ─║╦ą─Ż¼╦³▓╗āHīŹ¼F┴╦ą┼╠¢╠Ä└ĒŻ¼Č°Ūę▀ĆīŹ¼F┴╦ī”─XļŖ▓╔╝»ļŖ┬ĘĄ─┐žųŲ║═VGA┐žųŲŲ„ĪŻFPGAķ_░l░Õ▓╔ė├Cyclone II EP2C35 DSPķ_░l░ÕŻ¼FPGAąŠŲ¼×ķCyclone II EP2C35F672ĪŻ

1 ŽĄĮyįOėŗ

1.1 ─XļŖ▓╔╝»ļŖ┬ĘĄ─įOėŗ

─XļŖą┼╠¢▒╚▌^╬ó╚§Ż¼Č°Ūęč═ø]į┌║▄ÅŖĄ─▒│Š░įļ┬Ģ║═Ė╔ö_ųąĪŻ▒žĒÜįOėŗ║Ž▀mĄ─ļŖ┬ĘŻ¼į┌Ę┼┤¾─XļŖą┼╠¢Ą─═¼ĢrŻ¼═©▀^×V▓©ęųųŲįļ┬ĢŻ¼╠ßĖ▀ą┼įļ▒╚Ż¼Ą├ĄĮ▌^║├Ą──ŻöM─XļŖą┼╠¢Ż¼▓ó═©▀^AD▐DōQ×ķ▀m║Žė┌FPGA╠Ä└ĒĄ─öĄūųą┼╠¢ĪŻ

▒Š╬─įOėŗĄ──XļŖ▓╔╝»ļŖ┬Ęų„ę¬░³└©ėąį┤ļŖśOĪóėę═╚“īäėļŖ┬ĘĪó─ŻöMļŖ┬ĘĪóöĄūųļŖ┬Ę║═ļŖį┤ĪŻėąį┤ļŖśOė├üĒé„ī¦─XļŖą┼╠¢Ż¼ėę═╚“īäėļŖ┬Ę┐╔ęįĮĄĄ═╣▓─ŻļŖē║ĪŻ─ŻöMļŖ┬Ę░³└©Ū░ų├Ę┼┤¾ļŖ┬ĘĪóĖ▀═©×V▓©ļŖ┬ĘĪóĘ┼┤¾×V▓©ļŖ┬Ę║═ļŖē║╠¦╔²ļŖ┬ĘŻ¼īŹ¼F─ŻöMą┼╠¢š{└Ē║═ą┼įļ▒╚Ą─╠ßĖ▀ĪŻöĄūųļŖ┬Ę░³└©AD▐DōQļŖ┬Ę║═╣Ō±ŅĖ¶ļxļŖ┬ĘŻ¼ų„ę¬╣”─▄╩Ū─ŻöMą┼╠¢ĄĮöĄūųą┼╠¢Ą─▐DōQĪŻ

1.2 ╗∙ė┌FPGAĄ─VGAęĢėX┤╠╝żŲ„Ą─įOėŗ

─XÖCĮė┐┌ęĢėX┤╠╝żŲ„═©│Ż┐╔ęįį┌ėŗ╦ŃÖC’@╩ŠŲ„╗“ļŖęĢÖC╔Ž═©▀^ė▓╝■║═▄ø╝■ā╔ĘNĘĮ╩Į«a╔·Ż¼ę▓┐╔ęįįOėŗīŻķTĄ─łDą╬’@╩ŠļŖ┬Ę[4]ĪŻ▓╔ė├ė▓╝■īŹ¼FęĢėX┤╠╝żŻ¼ūŅ┤¾ā׳c╩Ūąį─▄ĘĆČ©Ż¼Ą½ą▐Ė─║═╔²╝ē▒╚▌^└¦ļyĪŻ

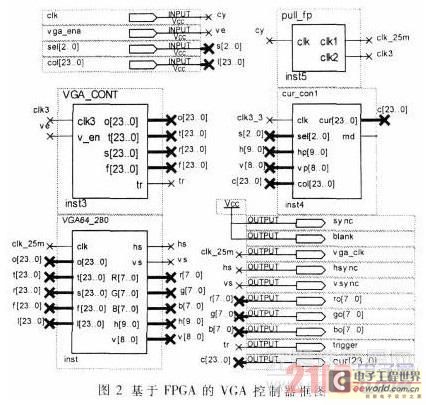

▒Š╬─Ą─ĘĮ░Ė╩Ū╗∙ė┌FPGAĄ─VGAęĢėX┤╠╝żŲ„Ż¼▓╔ė├VGA’@╩ŠŲ„ū„×ķęĢėX┤╠╝żŲ„Ż¼═©▀^VHDLŠÄ│╠Ą─ĘĮ╩Į«a╔·łDą╬┤╠╝żą┼╠¢ĪŻFPGA╩Ūę╗ĘN░ļČ©ųŲļŖ┬ĘŻ¼Š▀ėą║▄ÅŖĄ─į┌ŠĆą▐Ė──▄┴”Ż¼┐╔ęįļSĢrą▐Ė─įOėŗČ°▓╗▒žĖ─äėė▓╝■ļŖ┬ĘĪŻę“┤╦Ż¼═©▀^ŠÄ│╠┐╔ęįņ`╗ŅĄž«a╔·▓╗═¼Ą─┤╠╝ż─Ż╩ĮŻ¼ą▐Ė─║═╔²╝ē╩«ĘųĘĮ▒ŃĪŻ░┤ššVGA’@╩ŠŲ„ųąąÆ▀├ĶĄ─╣żū„įŁ└Ē║═VGA╣żśIś╦£╩[5]Ż¼į┌FPGAųąįOėŗ┴╦VGA┐žųŲŲ„Ż¼░³└©ĘųŅl─ŻēKĪóÆ▀├ĶĢrą“«a╔·─ŻēKĪółDŽ±├Ķ╩÷─ŻēKĪó┤╠╝żŅl┬╩┐žųŲ─ŻēK║═╣Ōś╦┐žųŲ─ŻēKŻ¼Ųõ┐“łD╚ńłD2╦∙╩ŠĪŻ

ĘųŅl─ŻēK«a╔·Ž±╦ž▌ö│÷Ņl┬╩║═┤╠╝ż╦∙ąĶĄ─Ņl┬╩ĪŻCycloneó“EP2C35ąŠŲ¼Š▀éõ4éĆį÷ÅŖą═ŪČ╚ļ╩ĮµiŽÓŁh(PLL)Ż¼├┐éƵiŽÓŁh┐╔ęį╠ß╣®3éĆ▌ö│÷ĢrńŖŻ¼Ņl┬╩ĘŪ│ŻĘĆČ©Ż¼▀Ć┐╔ęįĘųŅl║═▒ČŅlĪŻė├µiŽÓŁhIP║╦š{ė├ŪČ╚ļ╩ĮµiŽÓŁhŻ¼ų▒ĮėĘųŅl«a╔·Ž±╦ž▌ö│÷Ņl┬╩Ż¼▒ŻūC┴╦ŽĄĮyĢrńŖĄ─Š½┤_║═ĘĆČ©ĪŻėŗöĄŲ„ĘųŅlĄ├ĄĮ┤╠╝ż╦∙ąĶĄ─Ņl┬╩Ż¼┐╔«a╔·▓╗═¼Ą─┤╠╝żŅl┬╩ĪŻ

Æ▀├ĶĢrą“«a╔·─ŻēK╠ß╣®VGAąąÆ▀├Ķ║═ł÷Æ▀├ĶĄ─Ģrą“ĪŻī”Ž±╦ž▌ö│÷Ņl┬╩ėŗöĄĘųŅlŻ¼«a╔·ąąÆ▀├ĶŅl┬╩Ż¼ŲõŅl┬╩×ķ31.469 kHzĪŻ╚╗║¾Ż¼ī”ąąÆ▀├ĶŅl┬╩ėŗöĄĘųŅlŻ¼Ą├ĄĮł÷Æ▀├ĶŅl┬╩,Ųõł÷Ņl×ķ59.94 HzĪŻ

łDŽ±├Ķ╩÷─ŻēK├Ķ╩÷ąĶꬫa╔·Ą─┤╠╝żłDą╬,ę║Š¦├µ░Õū▀ä▌░³└©╬╗ė┌Ų┴─╗╔ŽŽ┬ū¾ėę4éĆĘĮŽ“Ą─4éĆĘĮēK║═0Īó1Īó2Īó3öĄūųĪŻ4éĆĘĮēK╩ŪīŹ¼FČÓĒŚ─┐ś╦▀xō±Ą─┤╠╝ż─┐ś╦Ż¼╣Ōś╦ė├üĒĘ┤ü▀xō±Ą─ĮY╣¹ĪŻ═©▀^ąąū°ś╦║═ł÷ū°ś╦üĒ├Ķ╩÷ĘĮēK║═öĄūųĄ─╬╗ų├╝░┤¾ąĪĪŻį┌ĘĮēK╔Žś╦ūóöĄūųŻ¼ęįģ^äe▓╗═¼Ą─ĘĮēKĪŻłDą╬Ą─Ė─ūā╗“▀\äė┐╔ę²Ųėąą¦Ą─šT░lļŖ╬╗Ż¼ę“┤╦Ż¼ĘĮēKĄ─Ņü╔½╩Ū║┌╔½║═░ū╔½Į╗╠µūā╗»Ą─ĪŻ×ķ┴╦╩╣ĘĮēKĖ³’@ų°Ż¼Ąū╔½▓╔ė├╔Ņ╩»░Õ╗ę╔½ĪŻ

┤╠╝żŅl┬╩┐žųŲ─ŻēKįOėŗ┴╦┤╠╝żĄ──Ż╩ĮĪŻ▓╔ė├═¼Ņl┤╬Å═║Ž┤╠╝żĘĮ╩ĮŻ¼╝┤į┌å╬╬╗Ģrķgā╚Ė„éĆęĢėX┤╠╝ż─ŻēKķWĀqĄ─┤╬öĄŽÓ═¼Ż¼Ą½Ė„éĆ┤╠╝ż─ŻēKķWĀqĄ─Ģr┐╠ŽÓ╗źÕeķ_ĪŻ═©▀^ėŗöĄŲ„ĘųŅl«a╔·─ŻēKķWĀqĄ─ĢrńŖĪŻķWĀqĢr┐╠Ą─Õeķ_ė├ŽÓ╬╗čėĢrīŹ¼F,ė├ŽĄĮyĢrńŖ«a╔·ę╗éĆėŗöĄŲ„Ż¼Ė∙ō■ėŗöĄŲ„Ą─ėŗöĄ┐žųŲčėĢrŻ¼▀_ĄĮŠ½┤_Č©ĢrĄ─ę¬Ū¾ĪŻ«öķWĀqĄ─ĢrńŖą┼╠¢×ķĄ═ļŖŲĮĢrŻ¼ĘĮēK×ķ║┌╔½;×ķĖ▀ļŖŲĮĢrŻ¼ĘĮēK×ķ░ū╔½ĪŻį┌┤╠╝ż─ŻēK║┌ūā░ūĄ─═¼ĢrŻ¼░l│÷ė|░lą┼╠¢ĪŻ

╣Ōś╦┐žųŲ─ŻēK├Ķ╩÷╣Ōś╦Ą─łDą╬Ż¼┐žųŲ╣Ōś╦Ą─ęŲäėĪŻ═©▀^Ė─ūā╣Ōś╦Ą─ū°ś╦║═ĘųŅlüĒ┐žųŲ╣Ōś╦ęŲäėĄ─ĘĮŽ“║═╦┘Č╚ĪŻ╣Ōś╦Ą─Ņü╔½×ķ╝t╔½ĪŻ

╗∙ė┌FPGAĄ─VGAęĢėX┤╠╝żŲ„│õĘų└¹ė├┴╦FPGA░ļČ©ųŲļŖ┬ĘĄ─╠ž³cŻ¼▓╔ė├═¼▓ĮĢrą“įOėŗĘĮ╩ĮŻ¼▓╗Ą½ąį─▄ĘĆČ©Ż¼Č°Ūę─▄Ė∙ō■ąĶę¬ņ`╗ŅĄžįOėŗ▓╗═¼Ą─ęĢėX┤╠╝żŲ„ĪŻ╦³īŹ¼FĘĮ▒ŃŻ¼╣”─▄ÅŖ┤¾Ż¼╝µŠ▀ė├ė▓╝■╗“▄ø╝■ĘĮ╩ĮīŹ¼FęĢėX┤╠╝żŲ„Ą─ā׳cĪŻ

1.3 ╦▓æBęĢėXšT░lļŖ╬╗Ą─╠ß╚Ī┼cūRäe

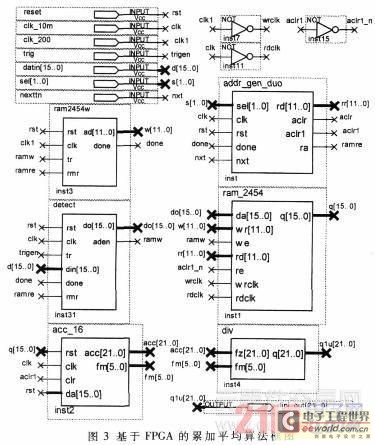

└█╝ėŲĮŠ∙ĘĮĘ©╩ŪūŅĮøĄõĄ─šT░lļŖ╬╗ą┼╠¢╠Ä└ĒĘĮĘ©Ż¼ę▓╩ŪļŖ╔·└Ē£y┴┐ųą╠ßĖ▀ą┼įļ▒╚ūŅ│Żė├Ą─ĘĮĘ©[2]ĪŻį┌FPGAųąįOėŗĄ─└█╝ėŲĮŠ∙╦ŃĘ©Ą─┐“łD╚ńłD3╦∙╩ŠŻ¼░³└©ė|░lą┼╠¢Öz£y─ŻēKĪóRAMĄžųĘ┐žųŲ─ŻēKĪó«É▓Įļp┐┌RAMĪó└█╝ėŲ„║═│²Ę©Ų„ĪŻ

ė|░lą┼╠¢Öz£y▒ŻūC┴╦┤╠╝ż┼cęĢėXšT░lļŖ╬╗Ą─µiĢr═¼▓ĮĻPŽĄĪŻų╗ėąÖz£yĄĮūŅįńķWĀqĄ─┤╠╝ż─ŻēKĄ─ė|░lą┼╠¢Ż¼▓┼░č─XļŖöĄō■┤µā”ĄĮRAMųąĪŻ«ö▀_ĄĮę¬Ū¾Ą─ķWĀq┤╬öĄĢrŻ¼═Żų╣öĄō■Ą─īæ╚ļĪŻĖ∙ō■┤╠╝ż─ŻēKų«ķgĄ─čėĢrĻPŽĄŻ¼┐╔ęį┤_Č©┼cĖ„éĆ┤╠╝ż─ŻēKŽÓæ¬Ą─öĄō■į┌RAMųąĄ─Ų╩╝ĄžųĘĪŻ╚╗║¾Ż¼░┤ššŲ╩╝ĄžųĘūx│÷öĄō■Įo└█╝ėŲ„Ż¼└█╝ėĄ─┤╬öĄ┼cķWĀq┤╬öĄŽÓ═¼ĪŻūŅ║¾Ż¼ė├│²Ę©Ų„│²ęį└█╝ėĄ─┤╬öĄŻ¼Ą├ĄĮ└█╝ė║¾Ą─ŲĮŠ∙ĮY╣¹.

ų¬ūR«aÖÓ(IP)║╦Ż¼╩ŪųĖ╝║“×ūCĄ─Īó┐╔ųž└¹ė├Ą─ĪóŠ▀ėą─│ĘN┤_Č©╣”─▄Ą─IC─ŻēKĪŻFPGAėą┤¾┴┐Ė„ĘNė├═ŠĄ─IP║╦ĪŻ▀@ą®IP║╦ī”ā╚║╦▀Mąą┴╦ģóöĄ╗»Ż¼═©▀^Ņ^╬─╝■╗“łDą╬ė├æ¶Įė┐┌(GUI)┐╔ęįĘĮ▒ŃĄžī”ģóöĄ▀Mąą▓┘ū„ĪŻ═©▀^«É▓Įļp┐┌RAM IP║╦š{ė├Ų¼ā╚RAMüĒŠÅ┤µ─XļŖöĄō■Ż¼▒ŻūC┴╦öĄō■Įė┐┌Ą─═¼▓Į║═öĄō■╠Ä└Ē╦┘Č╚ĪŻė├└█╝ėŲ„IP║╦║═│²Ę©Ų„IP║╦üĒīŹ¼F╦ŃĘ©ųąĄ─└█╝ėŲ„║═│²Ę©Ų„ĪŻ

ų╗▓╔ė├└█╝ėŲĮŠ∙Ą─ĘĮĘ©, ąĶę¬▀Mąą╔Ž░┘┤╬▓┼─▄Ą├ĄĮ┐╔┐┐Ą─šT░lļŖ╬╗▓©ą╬, ą┼╠¢╠ß╚ĪĄ─Ģrķg╠½ķLĪŻį┌╔┘┴┐┤╬└█╝ėŲĮŠ∙ĢrŻ¼×ķ┴╦▀Mę╗▓Į╠ßĖ▀ą┼įļ▒╚Ż¼╠ß╚Ī│÷▌^×ķ└ĒŽļĄ─šT░lļŖ╬╗▓©ą╬Ż¼▓╔ė├öĄūų×V▓©Ą─ĘĮĘ©üĒ£p╔┘įļ┬ĢĄ─ė░ĒæĪŻFIR×V▓©Ų„Š▀ėąć└Ė±Ą─ŠĆąįŽÓ╬╗Ż¼ĘĆČ©ąį║├Ż¼Č°Ūę═©ŅlĦ▒╚▌^ŲĮ╠╣ĪŻ╦∙ęįŻ¼▓╔ė├FIR×V▓©Ų„üĒīŹ¼FöĄūų×V▓©ĪŻė├┤░║»öĄįOėŗĘ©įOėŗę╗éĆ15ļAĄ─Ą══©FIR×V▓©Ų„Ż¼┤░║»öĄ×ķ║Ż├„┤░Ż¼Įžų╣Ņl┬╩×ķ10 HzĪŻ└¹ė├MATLAB╣żŠ▀ŽõųąĄ─FDAToolįOėŗ×V▓©Ų„Ż¼▓ó▐DōQ×ķHDL┤·┤aŻ¼┐╔ęį║▄ĘĮ▒ŃĄžį┌FPGAųąīŹ¼FFIR×V▓©Ų„ĪŻ═©▀^š{ė├Cyclone󓹊Ų¼ųąė├ė┌DSP▀\╦ŃĄ─ŪČ╚ļ╩Į│╦Ę©Ų„üĒīŹ¼FFIR×V▓©ųąĄ─│╦Ę©▀\╦ŃĪŻ┼c╗∙ė┌▀ē▌ŗå╬į¬Ą─│╦Ę©Ų„ŽÓ▒╚Ż¼ŪČ╚ļ╩Į│╦Ę©Ų„ąį─▄Ė³Ė▀Ż¼š╝ė├▀ē▌ŗå╬į¬Ė³╔┘ĪŻŪČ╚ļ╩Į│╦Ę©Ų„─▄ē“┼cCycloneó“Ų„╝■Ą─M4K RAMēK▀Mąą¤o┐p╝»│╔Ż¼īŹ¼FĖ▀ą¦Ą─DSP╦ŃĘ©[6]ĪŻ

╦▓æBęĢėXšT░lļŖ╬╗Ą─ūRäeŻ¼Š═╩Ūę¬īóšT░lļŖ╬╗ą┼╠¢▐DōQ│╔ę╗ŽĄ┴ą┐žųŲ├³┴ŅŻ¼Å─Č°īŹ¼F╚╦─X┼c═ŌĮńĄ─═©ą┼┼c┐žųŲĪŻ─Ż░ÕŲź┼õ╩Ūé„ĮyĄ──Ż╩ĮūRäeĘĮĘ©ų«ę╗ĪŻŽÓĻPŽĄöĄ╩Ūūā┴┐ų«ķgŽÓĻP│╠Č╚Ą─ųĖś╦Ż¼┐╔ęįė├ė┌┼ąöÓŪ·ŠĆöM║Ž│╠Č╚ĪŻė├ŽÓĻPŽĄöĄüĒ║Ō┴┐─Ż░Õ┼c╬┤ų¬─Ż╩ĮŲź┼õĄ─║├ē─Ż¼╩Ūę╗éĆėąą¦Ūę┐╔ąąĄ─ĘĮĘ©ĪŻ

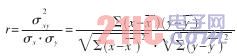

╩ūŽ╚,▀xČ©ę╗éĆ╠žš„├„’@Ą─╦▓æBęĢėXšT░lļŖ╬╗▓©ą╬Ż¼ū„×ķ─Ż░ÕŲź┼õĄ─ģó┐╝─Ż░Õ;╚╗║¾Ż¼░čīŹĢr╠ß╚ĪšT░lļŖ╬╗▓©ą╬┼cģó┐╝─Ż░Õū÷ŽÓĻPŽĄöĄėŗ╦ŃĪŻ╚¶ŽÓĻPŽĄöĄųĄ┤¾ė┌įOČ©Ą─ķōųĄĢrŻ¼Š═šJ×ķÖz£yĄĮ┴╦Ą─šT░lļŖ╬╗Ż¼░l│÷┐žųŲ├³┴ŅŻ¼╩╣╣Ōś╦ęŲŽ“ŽÓæ¬Ą─┤╠╝ż─ŻēKŻ¼Å─Č°īŹ¼F╦▓æBęĢėXšT░lļŖ╬╗Ą─ūRäeĪŻ

ŽÓĻPŽĄöĄĄ─ėŗ╦Ń╣½╩Į╚ńŽ┬Ż║

╝┘Č©─Ż░ÕĄ─öĄō■×ķyŻ¼┐╔ęįŽ╚ļxŠĆėŗ╦Ń│÷╣½╩Į(1)ųą║¼yĒŚĄ─ųĄŻ¼┤µį┌ROMųąŻ¼Å─Č°╠ßĖ▀īŹĢrėŗ╦ŃĄ─╦┘Č╚ĪŻų╗ąĶę¬1éĆ│╦╝ėŲ„IP║╦Ż¼š{ė├FPGAąŠŲ¼ųąĄ─ŪČ╚ļ╩Į│╦Ę©Ų„Ż¼Š═┐╔ęįīŹ¼FĘųūė║═Ęų─ĖųąĄ─│╦╝ė▀\╦ŃŻ¼╣Ø╩Ī┴╦Ų„╝■Ą─┘Yį┤ĪŻė├ķ_Ė∙╠¢IP║╦üĒīŹ¼Fķ_Ė∙╠¢▀\╦ŃĪŻ

FPGA▀\ąą╦┘Č╚┐ņŻ¼ā╚▓┐│╠ą“▓óąą▀\ąąŻ¼▓óŪęėąDSP▀\╦ŃIP║╦║═ŪČ╚ļ╩Į│╦Ę©Ų„Ż¼─▄ē“┐ņ╦┘£╩┤_Ąž═Ļ│╔─XļŖ╠Ä└Ē╦ŃĘ©Ż¼ØMūŃą┼╠¢╠Ä└ĒĄ─īŹĢrąįę¬Ū¾ĪŻ

2 īŹ“×ĮY╣¹

▓╔ė├▒Š╬─ĘĮ░ĖśŗĮ©Ą──XÖCĮė┐┌ŽĄĮy▀MąąīŹ“×ĪŻę║Š¦├µ░Õū▀ä▌─XÖCĮė┐┌īŹ“×═©│Ż×ķę╗ĮMīŹ“ׯ¼Ęųäe▀xō±▓╗═¼Ą─4éĆ┤╠╝ż─ŻēK(░³└©╚½▓┐─┐ś╦Ą─▀xō±)ĪŻį┌īŹ“×ųąŻ¼╩▄įćš▀Ņ^┤„ļŖśO├▒Ż¼č█Š”ŠÓŲ┴─╗70 cmū¾ėęŻ¼┐žųŲ╣Ōś╦ęŲŽ“╦∙ūóęĢĄ──┐ś╦ĪŻ├┐┤╬īŹ“×ĢrŻ¼4éĆ┤╠╝ż─ŻēK═Ļ│╔ę╗▌åķWĀq║¾Ż¼╚╗║¾═ŻŅDÄū├ļŻ¼▀MąąŽ┬ę╗▌åķWĀqĪŻ4▌åķWĀqŻ¼╝┤4éĆ┤╠╝ż─ŻēKČ╝─▄▒╗▀xųą║¾Ż¼ūįäė═Żų╣ķWĀqĪŻ

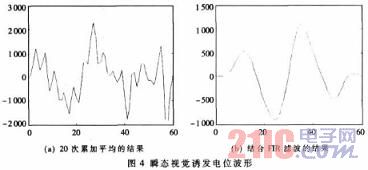

īŹ“×ųą╠ß╚ĪĄ─╦▓æBęĢėXšT░lļŖ╬╗▓©ą╬╚ńłD4╦∙╩ŠĪŻłD4(a)ųąŻ¼ęčĮø┐╔ęį┐┤ĄĮęĢėXšT░lļŖ╬╗Ą─ļrą╬Ż¼Ą½ęĢėXšT░lļŖ╬╗Ą─╠žš„▓╗╩Ū╩«Ęų├„’@ĪŻłD4(b)ųąŻ¼ė├FIR×V▓©ī”šT░lļŖ╬╗ą┼╠¢▀Mę╗▓Į╠Ä└ĒŻ¼Ą├ĄĮ┴╦╠žš„▒╚▌^├„’@Ą─ęĢėXšT░lļŖ╬╗ĪŻ

─XÖCĮė┐┌Ą─īŹ“×ĮY╣¹╚ń▒Ē1╦∙╩ŠŻ¼╩▄įćš▀╩Ū5├¹ĮĪ┐Ą─ąąįĪŻš²┤_┼ąöÓĢrŻ¼į┌┤╠╝ż─ŻēK═Żų╣ķWĀqĄ─═¼ĢrŻ¼╣Ōś╦┴ó┐╠ęŲŽ“╩▄įćš▀ūóęĢĄ──ŻēKĪŻ

╗∙ė┌╦▓æBęĢėXšT░lļŖ╬╗Ą──XÖCĮė┐┌īŹ“×▒Ē├„Ż¼▒Š╬─Įo│÷Ą─╗∙ė┌ę║Š¦├µ░Õū▀ä▌FPGAĄ──XÖCĮė┐┌īŹĢrŽĄĮyĄ─ĘĮ░Ė╩Ū┐╔ąąĄ─ĪŻ╗∙ė┌FPGAĄ─VGAęĢėX┤╠╝żŲ„Ż¼┤╠╝żŅl┬╩╩«ĘųĘĆČ©Ż¼┤╠╝żĮń├µęūė┌Įė╩▄Ż¼ą▐Ė─╔²╝ēĘĮ▒ŃĪŻ╗∙ė┌FPGAĄ──XļŖą┼╠¢╠Ä└Ē╦ŃĘ©Ż¼▓╔ė├╔┘┴┐┤╬└█╝ėŲĮŠ∙ĮY║ŽFIR×V▓©üĒ╠ß╚ĪšT░lļŖ╬╗Ż¼▓ó═©▀^─Ż░ÕŲź┼õĄ─ĘĮĘ©╝ėęįūRäeŻ¼┐╔ęį┐ņ╦┘£╩┤_Ąž░č╦▓æBšT░lļŖ╬╗ą┼╠¢▐DōQ×ķ┐žųŲ├³┴ŅŻ¼īŹ¼F┴╦īŹĢrĄ──XÖCĮė┐┌ŽĄĮyĪŻ╗∙ė┌FPGAĄ──XÖCĮė┐┌ŽĄĮyŻ¼╩Ūę╗ĘNą┬Ą─ĘĮĘ©Ż¼ę▓╩Ūī”ę║Š¦├µ░Õū▀ä▌─XÖCĮė┐┌īŹ¼FĘĮĘ©Ą─ėąęµ╠Į╦„ĪŻ