š¬ę¬Ż║PCIe┐éŠĆ▓╗āHė▓╝■Įė┐┌║åå╬Ż¼▄ø╝■║═PCI┐éŠĆ═Ļ╚½╝µ╚▌Ż¼Č°Ūęé„▌ö╦┘Č╚öĄ╩«▒Čė┌PCI┐éŠĆĪŻßśī”▌dÖC╚╬䚎ĄĮyīŹĢręĢŅl▓╔╝»ėøõøĄ─ąĶŪ¾Ż¼įOėŗ┴╦ę╗ĘN╗∙ė┌PCIe┐éŠĆĄ─║Į┐šęĢŅl▓╔╝»ėøõøŽĄĮyŻ¼└¹ė├¼Fł÷┐╔ŠÄ│╠▀ē▌ŗŲ„╝■(FPGA)īŹ¼F┴╦ęĢŅlöĄō■┴„Ą─ŠÄĮŌ┤a║═PCIeś“Įė┐┌Ą─įOėŗŻ¼║å╗»┴╦ė▓╝■Įė┐┌įOėŗŻ¼╠ßĖ▀┴╦ŽĄĮyĄ─╣żū„ą¦┬╩ĪŻŽĄĮyį┌─│ą═öĄūų╗»ī”┐╣ė¢ŠÜŽĄĮyųąĄ─īŹļHæ¬ė├▒Ē├„įōįOėŗīŹė├┐╔ąąĪŻ

0 ę²čį

║Į┐šļŖūėŽĄĮyų«ķgęįé„▀fĀŅæBöĄō■║═┐žųŲöĄō■×ķų„Ż¼ę“×ķöĄō■┴┐▓╗╩«ĘųŠ▐┤¾Ż¼ī”é„▌ö╦┘┬╩ę¬Ū¾▓ó▓╗Ė▀ĪŻ└²╚ńŻ¼ūŅ┴„ąąĄ─║Į┐š┐éŠĆARINC 429║═1553B┐éŠĆŻ¼╦┘┬╩Ęųäe╩Ū100kbps║═1MbpsĪŻČ°ļSų°’wąąė¢ŠÜÅŖČ╚║═Š½Č╚Ą─╠ßĖ▀Ż¼’wąąįć“×║═ė¢ŠÜ▀^│╠Ą─ČÓ═©Ą└ęĢŅl«ŗ├µąĶę¬īŹĢrėøõøŽ┬üĒęį▒Ń▀Mąą╩┬║¾Ęų╬÷įu╣└║═ŽĄĮyįOėŗĖ─▀MĪŻ┼cé„▌öĀŅæB┐žųŲą┼ŽóŽÓ▒╚Ż¼▀@ą®ęĢŅlöĄō■╩ŪŠ▐┴┐Ą─Ż¼ī”║ĮļŖŽĄĮyĄ─║Ż┴┐┤µā”║═öĄō■Ė▀╦┘é„▌öČ╝╠ß│÷┴╦Ė³Ė▀Ą─ę¬Ū¾ĪŻ▒Š╬─╠ß│÷ę╗ĘN║Į┐šęĢŅl▓╔╝»ėøõøŽĄĮyĄ─įOėŗĘĮ░ĖŻ¼▓╔ė├╦┘┬╩Ė▀▀_2.5GbpsĄ─PCIe┐éŠĆśŗĮ©ŽĄĮyŻ¼PCIe┐éŠĆ╝╚ėąĖ▀╦┘Ą─öĄō■é„▌ö─▄┴”Ż¼ėųėą┴╝║├Ą─═ŌįOĮė┐┌Ż¼ėą└¹ė┌┤¾╚▌┴┐ą┼╠¢Ą─īŹĢré„▌öĪŻėąą¦ĮŌøQ┴╦ÖC▌dČÓ═©Ą└ęĢŅlöĄō■Ą─īŹĢr▓╔╝»┼cėøõøŻ¼×ķ║Į┐šė¢ŠÜ╚╬䚎ĄĮyĄ─╩┬║¾įu╣└║═ąį─▄Ęų╬÷Ė─▀M╠ß╣®┴╦▒ŃĮ▌Ą─╩ųČ╬ĪŻ

1 ŽĄĮyĄ─ĘĮ░ĖįOėŗ

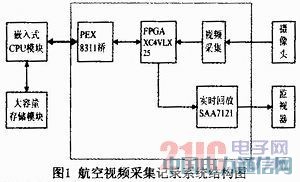

į┌║Į┐šęĢŅl▓╔╝»ėøõøŽĄĮyųąŻ¼özŽ±Ņ^░č▌dÖC╚╬䚎ĄĮyĄ─īŹĢr«ŗ├µęĢŅlöĄō■░┤ŅAČ©Ė±╩ĮĮMļŻ¼═©▀^LVDSą┼╠¢┐éŠĆé„▌öĮoęĢŅl▓╔╝»─ŻēKŻ╗Įø▀^ęĢŅl▓╔╝»─ŻēKī”LVDSą┼╠¢ļŖŲĮ▀MąąūāōQ╠Ä└Ē║¾Ż¼īóå╬Č╦ęĢŅlöĄūųą┼╠¢╦═Įo┐╔ŠÄ│╠▀ē▌ŗŲ„╝■(FPGA)▀MąąęĢŅlĮŌ┤a╠Ä└ĒĪŻĮŌ┤a║¾Ą─öĄūųęĢŅlŻ¼ę╗ĘĮ├µ═©▀^SAA7121ęĢŅlŠÄ┤aŲ„ų▒Įė╦═Įo▒OęĢŲ„Ż¼ūī’wąąåTīŹĢršŲ╬šė¢ŠÜŪķør┼cą¦╣¹Ż║┴Ēę╗ĘĮ├µ═©▀^Ė▀╦┘PCIe┐éŠĆé„╦═ĮoŪČ╚ļ╩ĮCPU─ŻēK▀MąąęĢŅlöĄō■ē║┐s┤µā”Ż¼╣®╩┬║¾Ęų╬÷ĪŻ║Į┐šęĢŅl▓╔╝»ėøõøŽĄĮy┐é¾wĮYśŗ╚ńłD1╦∙╩ŠĪŻ

2 ŽĄĮyĄ─ė▓╝■įOėŗ

ŽĄĮyĄ─ė▓╝■įOėŗų„ę¬╝»ųąį┌Ė„éĆ╣”─▄─ŻēKĄ─ļŖ┬ĘįOėŗ╔ŽŻ¼╩Ū▄ø╝■įOėŗ║═ŽĄĮyš{įćĄ─ŲĮ┼_╗∙ĄAĪŻė▓╝■įOėŗæ¬įō▒ŻūCŽĄĮy▀\ąąĄ─Ė▀┐╔┐┐ąįŻ¼į┌ØMūŃę¬Ū¾Ą─Ū░╠ߎ┬Ż¼▒M┴┐£p╔┘┐╔ŠÄ│╠▀ē▌ŗĪóŽĄĮy▄ø╝■Ą─įOėŗ┼cš{įćĄ─ļyČ╚ĪŻ

2.1 ęĢŅlöĄō■▓╔╝»

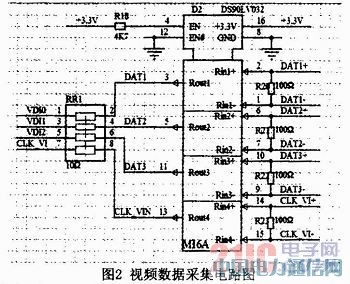

özŽ±Ņ^özõøĄ─ęĢŅlöĄō■ęįLVDS▓ŅĘųļŖŲĮą┼╠¢▀Mąąé„▌öŻ¼ąĶę¬▀MąąļŖŲĮą┼╠¢▐DōQ▓┼─▄▀Mąą║¾└męĢŅlą┼╠¢Ą─ėøõø╠Ä└ĒĪŻözŽ±Ņ^é„▌öĄ─ęĢŅlöĄō■░³└©4ī”LVDS▓ŅĘųą┼╠¢Ż¼CLK+/CLK-╩Ū▓╔╝»öĄō■Ą─ĢrńŖŻ¼ŲõėÓ3ī”▓ŅĘųą┼╠¢░³║¼ų°Ž±╦ž╗ęČ╚ĪŻ▓ŅĘųą┼╠¢Įø▀^DS90LV032▐DōQŻ¼ūā│╔4éĆå╬Č╦Ą─öĄūųą┼╠¢Ż¼╣®║¾├µĄ─ļŖ┬Ę╠Ä└ĒĪŻęĢŅl▓╔╝»ļŖ┬Ę╚ńłD2╦∙╩ŠĪŻ

ę“×ķęĢŅlöĄō■Ņl┬╩▌^Ė▀Ż¼Įø▀^▐DōQ║¾Ą─å╬Č╦ą┼╠¢æ¬įōČ╦Įė10ΩĄ─ļŖūĶęįęųųŲĘ┤╔õŻ¼╠ßĖ▀ą┼╠¢ĘĆČ©ąįĪŻ

2.2 ęĢŅlĮŌ┤a║═╠Ä└Ē

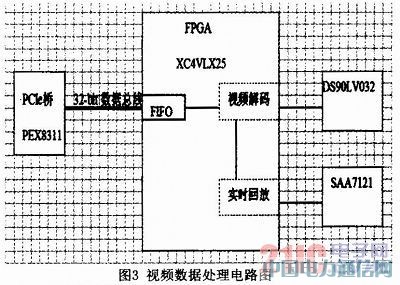

ī”Ū░Č╦▓╔╝»Ą─ęĢŅlöĄō■Ż¼▒žĒÜ▀Mąą╠Ä└Ē▓┼─▄īŹĢr’@╩Š║═ē║┐s┤µā”ĪŻė╔ė┌ęĢŅlöĄō■┴┐┤¾Ż¼×ķ▀_ĄĮūŅ┴„Ģ│Ą─┐ņ╦┘╠Ä└ĒŻ¼æ¬įōė╔ė▓╝■▀ē▌ŗų▒Įė▀MąąöĄō■╠Ä└ĒĪŻęĢŅlöĄō■Ą─ĮŌ┤a║═╠Ä└Ēų„ę¬ė╔FPGA═Ļ│╔Ż¼ę▓╩Ū┐╔ŠÄ│╠▀ē▌ŗįOėŗĄ─ų„ę¬╚╬äšĪŻ

«öŪ░Č╦DS90LV032īóĮø▀^ą┼╠¢▐DōQęį║¾Ą─ęĢŅlöĄō■é„▌öĮoFPGAŻ¼ė╔FPGA═Ļ│╔ęĢŅlą┼╠¢Ą─ĮŌ┤a▀ĆįŁĪóĖ±╩Į▐DōQ║¾═¼▓Įé„▌öĮoCPU─ŻēK▀MąąīŹĢrėøõø║═īŹĢr╗žĘ┼ęĢŅl─ŻēKĪŻFPGAęĢŅlöĄō■╠Ä└ĒĄ─ė▓╝■Įė┐┌įOėŗ╚ńłD3╦∙╩Š

2.3 ęĢŅlöĄō■╗žĘ┼

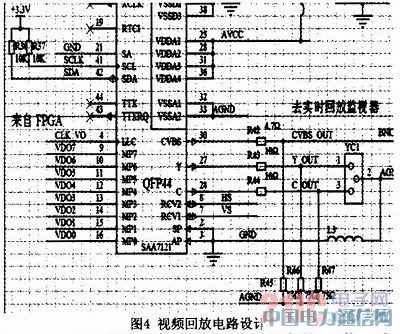

ęĢŅl╗žĘ┼╩ŪĘĮ▒Ń’wąąåT─▄ē“īŹĢr▒O┐žė¢ŠÜ║═įć“ץ─ŪķørĪŻŽĄĮy▓╔ė├Philips╣½╦ŠĄ─SAA7121ęĢŅlŠÄ┤aŲ„Ż¼īóFPGA╠Ä└Ē║¾Ą─ęĢŅlöĄō■▐DōQ×ķPALųŲĄ─ŠC║ŽęĢŅlŻ¼╦═Įo’wąąåT├µŪ░Ą─▒OęĢŲ„▀Mąą’@╩ŠĪŻ╚ńłD4╦∙╩ŠĪŻ

SAA7121ąĶę¬▀Mąą│§╩╝╗»┼õų├║¾▓┼─▄╣żū„Ż¼│§╩╝╗»═©▀^įOų├ŠÄ┤aŲ„Ą─╝─┤µŲ„Ż¼┼õų├Ųõ╣żū„─Ż╩ĮĪŻ│§╩╝╗»ę¬═©▀^I2C┐éŠĆ═Ļ│╔Ż¼ŽĄĮyĄ─I2C┐éŠĆĮė┐┌ė╔FPGAīŹ¼FĪŻ═¼▓ĮĢrńŖCLK VO║═8-bit▓óąąęĢŅlöĄō■Č╝╩Ūė╔FPGAĮŌ┤a╠Ä└Ē║¾é„▌ö▀^üĒĄ─ĪŻŠÄ┤aŲ„Ą─╣żū„Ņl┬╩×ķ27MHzŻ¼FPGAĮŌ┤a║¾Ą─ęĢŅlöĄō■Įø▀^SAA7121ŠÄ┤aŲ„Ą─ŠC║ŽęĢŅlą┼╠¢CVBS╦═Įo▒OęĢŲ„ĪŻ═¼Ģrę▓įOėŗ┴╦ę╗éĆéõė├Ą─YCĘų┴┐ęĢŅlĮė┐┌ĪŻ

2.4 ęĢŅlé„▌ö

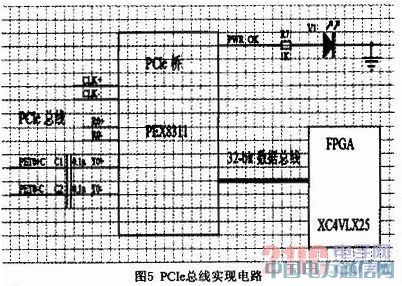

▓╔╝»Ą─ęĢŅlöĄō■Įø▀^FPGAĮŌ┤a╠Ä└Ē║¾ąĶę¬═©▀^PCIe┐éŠĆé„▌öĮoŪČ╚ļ╩ĮCPUęį▒Ńė┌īŹĢrē║┐s┤µā”ĪŻīŹ¼FĖ▀╦┘Ą─PCIe┐éŠĆ╩Ū║Ż┴┐öĄō■é„▌öĄ─ĻPµIĪŻöĄō■é„▌ö┐éŠĆ╝╝ąg╩Ū▓╗öÓĖ³ą┬░lš╣Ą─▀^│╠ĪŻį┌öĄō■═©ėŹĄ─Ų│§ļAČ╬Ż¼┤«ąą═©ėŹę“×ķą┼╠¢║åå╬ĪóīŹ¼FĘĮ▒ŃČ°æ¬ė├ÅVĘ║Ż¼š╝ėąĮyų╬Ąž╬╗Ż¼└²╚ńRS422┤«ąą═©ėŹŻ¼▒M╣▄╦┘┬╩▓╗Ė▀Ż¼─┐Ū░╚į╚╗║▄ėą╔·├³┴”ĪŻ×ķĮŌøQ┤«ąą═©ėŹĄ─Ų┐Ņiå¢Ņ}Ż¼ķ_╩╝▓╔ė├▓óąąé„▌ö┐éŠĆŻ¼▓óąą═©ėŹĄ─╦┘┬╩╚ĪøQė┌ĢrńŖŅl┬╩║═öĄō■īÆČ╚ĪŻ─┐Ū░ūŅ┴„ąą33MHz/32bitĄ─PCI┐éŠĆŻ¼ĘÕųĄé„▌ö╦┘┬╩┐╔▀_132MbpsĪŻ«ö└^└m╠ßĖ▀ĢrńŖŅl┬╩ĢrŻ¼▓óąą═©ėŹ┐éŠĆĄ─öĄō■īÆČ╚ģs│╔×ķ└^└m╠ßĖ▀╦┘┬╩Ą─šŽĄKĪŻė╔ė┌śOĖ▀ŅlŽ┬Ą─ŠĆ┬Ę┤«ö_║═Ę┤üŻ¼ļyęį▒ŻūCČÓ┬Ę▓óąą┐éŠĆą┼╠¢öĄō■═¼▓ĮĄ─ę╗ų┬ąįŻ¼öĄō■═©ėŹĄ─é„▌ö╝╝ągÅ─▓óąą╗žÜwĄĮ┤«ąąŻ¼▓óąąļpŽ“Ą─PCI┐éŠĆ░lš╣×ķ┤«ąąå╬Ž“Ą─PCIe┐éŠĆĪŻ╦┘┬╩Ė▀▀_2.5GbpsĄ─PCIe┐éŠĆėą╚²ī”▓ŅĘųą┼╠¢Ż¼╝┤═¼▓ĮĢrńŖCLK+/CLK-ĪóĮė╩šą┼╠¢R+/R-║═░l╦═ą┼╠¢T+/T-ĪŻPCIe┐éŠĆįOėŗļŖ┬Ę╚ńłD5╦∙╩ŠĪŻ

į┌PCIe▀@ĘNĖ▀╦┘ą┼╠¢é„▌ö┐éŠĆųąŻ¼öĄō■▓╗╩Ūų▒Įė═©▀^ą┼╠¢ī¦ŠĆĄ─ļŖē║ą┼╠¢Ż¼Č°╩Ū═©▀^Ė▀Ņl±Ņ║ŽĘĮ╩Įé„▌öĄ─ĪŻłD5ųąĄ─C1ĪóC2Š═╩Ū░l╦═ĘĮĄ─±Ņ║ŽļŖ╚▌Ż¼æ¬▒M┴┐┐┐Į³ś“Ų¼ĪŻ├┐ę╗ī”▓ŅĘųą┼╠¢Č╝æ¬įōėą±Ņ║ŽļŖ╚▌Ż¼łD5ųąĢrńŖ║═Įė╩šą┼╠¢ī”Ą─±Ņ║ŽļŖ╚▌Ż¼ļ[║¼į┌PCIeĄ─ų„┐žĘĮĪŻ

3 ŽĄĮyĄ─▀ē▌ŗįOėŗ

į┌ė▓╝■įOėŗĄ─╗∙ĄA╔ŽŻ¼▀ē▌ŗįOėŗ│╔×ķš¹éĆŽĄĮyąį─▄īŹ¼FĄ─ĻPµIĪŻ▀ē▌ŗįOėŗ═Ļ│╔š¹éĆŽĄĮyĄ─Ģrą“┐žųŲĪóęĢŅlöĄō■┴„Ą─▓╔╝»┼cĮŌ┤aĪóęĢŅl╗žĘ┼Ą─ŠÄ┤a║═PCIeś“Įė┐┌Ą─įOėŗĪŻ

3.1 ęĢŅlĮŌ┤a

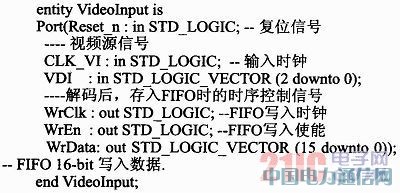

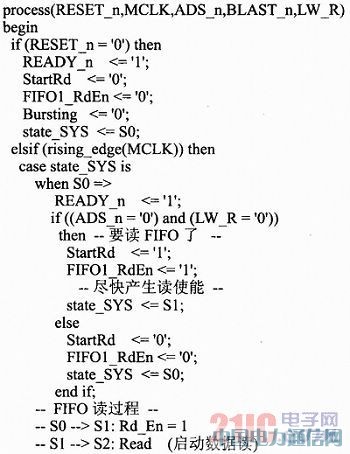

į┌▀ē▌ŗįOėŗųąŻ¼ęĢŅlĮŌ┤aĄ─╣”─▄╩ŪīóDS90LV032╦∙▐DōQĄ─å╬Č╦ą┼╠¢ĮŌ┤a║¾īæ╚ļFIFOŠÅø_Ż¼ė╔║¾└m▀ē▌ŗūx╚Ī╠Ä└ĒĪŻŲõ▀ē▌ŗĮė┐┌Ą─VHDLą╬╩Į├Ķ╩÷╚ńŽ┬Ż║

özŽ±Ņ^ū„×ķęĢŅlį┤Ż¼į┌├┐ę╗éĆCLKĄ─╔Ž╔²čž▌ö│÷ę╗éĆ3-bitöĄō■ĪŻ┼cų«ŽÓĘ┤Ż¼ĮŌ┤a▀ē▌ŗį┌CLKĄ─Ž┬ĮĄčžµi┤µę╗éĆ3-bitöĄō■Ż¼▀Mąą┴„╦«ŠĆµi┤µŻ¼ųžą┬▀ĆįŁęĢŅlĄ─╗ęČ╚öĄō■ĪŻī”ę╗éĆ16-bitĄ─öĄō■Ż¼╣▓ąĶ░l6┤╬ĪŻ

3.2 ęĢŅlŠÄ┤a

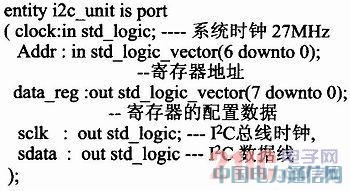

×ķų¦│ųSAA7121ŠÄ┤aŲ„Ż¼ęĢŅl╗žĘ┼▀ē▌ŗ░³└©×ķ│§╩╝╗»Č°╠ß╣®Ą─I2CĮė┐┌║═PALųŲĄ─ęĢŅlŠÄ┤aĪŻSAA7121Ą─╝─┤µŲ„╩Ū8-bitĄ─Ż¼ätŲõI2CĮė┐┌┐╔ęį├Ķ╩÷╚ńŽ┬Ż║

╔Žīė▀ē▌ŗš{ė├┤╦─ŻēKŻ¼├┐š{ė├ę╗┤╬Ż¼┼õų├ę╗éĆ╝─┤µŲ„ĪŻ╦∙ėą128éĆ╝─┤µŲ„Ą─┼õų├öĄō■╩ŪŅAŽ╚Č©ųŲĄ─Ż¼┤µĘ┼į┌│Ż┴┐öĄĮMųąĪŻ

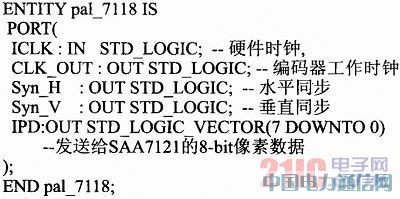

Įø▀^│§╩╝╗»║¾Ą─SAA7121┐╔ęįš²│Ż╣żū„┴╦ĪŻ┤╦Ģr▀ē▌ŗæ¬įō▓╗öÓ▌ö╦═ęĢŅlöĄō■ĪŻŲõ▀ē▌ŗĮė┐┌┐╔ęį├Ķ╩÷╚ńŽ┬Ż║

3.3 PCIeś“Įė┐┌įOėŗ

öĄō■Ė▀╦┘é„▌öų„ę¬¾w¼Fį┌PCIe┐éŠĆĄ─īŹļH═╠═┬┴┐Ż¼┤╦×ķĮŌ┤a║¾Ą─öĄō■é„▌öĄ─Ų┐ŅiĪŻ▀ē▌ŗįOėŗę¬╠žäe┐╝æ]ĄĮ▄ø╝■Ą─ĘĮ▒Ń║═Ė▀ą¦ĪŻĮė┐┌▀ē▌ŗįOėŗ╝»ųąį┌ųąöÓ▀ē▌ŗ║═öĄō■é„▌öĄ─burstĘĮ╩Į╔ŽĪŻ

ąĶę¬é„▌öĄ─ęĢŅlöĄō■Ż¼╩ūŽ╚╦═╚ļę╗éĆFIFOŻ¼īæ╚ļČ╦×ķ32k×16bitŻ¼ūx│÷Č╦×ķ16k×32bitŻ¼īæ╚ļĢr╝╚▀m║Ž┴╦ęĢŅlöĄō■Ą─īÆČ╚Ż¼ūx│÷é„▌öĢrėų░lō]┴╦PCI32-bit┐éŠĆĄ─ā×ä▌Ż¼╝ė┐ņ┴╦▐DōQĪŻųąöÓ▀ē▌ŗįOėŗ╚ńŽ┬Ż║

(1)«öīæ╚ļöĄō■▀_ĄĮFIFO╚▌┴┐Ą─1/4ĢrŻ¼╝┤īæē“4k×32bitĢr«a╔·ųąöÓĪŻ▀@éĆŚl╝■┐╔Ė∙ō■FIFOĄ─┐╔ŠÄ│╠┐š┼ąöÓŻ¼ęÓ╝┤PRG1 Empty=‘0’Ģr«a╔·ųąöÓĪŻ

(2)«öų„ÖCĒææ¬ųąöÓŻ¼ķ_╩╝ūxFIFOöĄō■Ģr│ĘõNųąöÓĪŻ

(3)«ö▒Š┤╬burstūxĮY╩°║¾Ż¼▓┼į╩įSĖ∙ō■Śl╝■ųžą┬┼ąöÓųąöÓŚl╝■ĪŻ

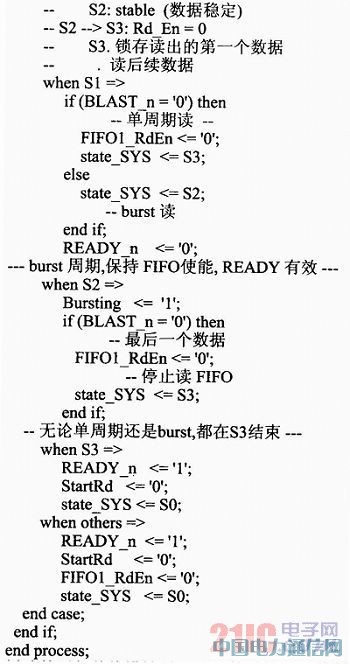

PCIeś“Įė┐┌Ą─▀ē▌ŗįOėŗūŅųžę¬Ą─▓┐Ęų╩Ū×ķ╦³Ą─Šų▓┐┐éŠĆ(Local bus)╠ß╣®¤o┐pĄ─š│║Ž▀ē▌ŗŻ¼ų¦│ųPCIeĄ─å╬┤╬įLå¢║═burstįLå¢ĪŻŲõĮė┐┌ĀŅæBÖC╚ńŽ┬Ż║

ś“Ų¼Ą─Šų▓┐┐éŠĆįOėŗ┴╦50MHzĄ─ĢrńŖŻ¼ī”32-bitöĄō■īÆČ╚Ż¼└Ēšō╔Ž┐╔ęį▀_ĄĮ200Mb/sĄ─═╠═┬┬╩ĪŻĮø▀^æ¬ė├▄ø╝■Ą─īŹ£yŻ¼┐╔ęį▀_ĄĮ143Mb/sĄ─╦┘┬╩Ż¼┐╝æ]ĄĮ▄ø╝■Ą─įSČÓķ_õNŻ¼▀@éĆ╦┘┬╩ęčĮø▒╚▌^└ĒŽļ┴╦ĪŻ

4 ŽĄĮyĄ─▄ø╝■įOėŗ

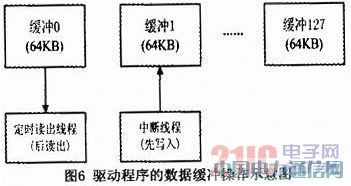

ŽĄĮyĄ─▄ø╝■įOėŗŲĮ┼_▓╔ė├WindowsXP EmbeddedŻ¼▄ø╝■Ęų×ķßśī”▒Šė▓╝■ŽĄĮyĄ─“īäė│╠ą“║═ęĢŅlē║┐s┼c╠Ä└ĒĄ─æ¬ė├│╠ą“ĪŻæ¬ė├│╠ą“░čęĢŅl┤µ×ķŲš═©▓źĘ┼Ų„─▄▓źĘ┼Ą─ęĢŅlĖ±╩ĮŻ¼├┐ļęĢŅl×ķ256ąą×256┴ą╣▓64KŽ±╦žĪŻį┌“īäė▄ø╝■ųąŻ¼«ö┤“ķ_įOéõĢrŻ¼╔Ļšłę╗ĮMŠÅø_Ż¼╣▓128éĆŠÅø_ĪŻ▀@éĆŠÅø_ī”æ¬ė├│╠ą“╩Ū═Ė├„Ą─Ż¼├┐éĆŠÅø_┐╔ęį┤µĘ┼ę╗éĆ═Ļš¹Ą─ęĢŅlļŻ¼╚ńłD6╦∙╩ŠĪŻ“īäė│╠ą“ųąėąā╔éĆų„ꬊĆ│╠Ż¼ųąöÓŠĆ│╠║═öĄō■ūx│÷ŠĆ│╠ĪŻ

į┌▀ē▌ŗįOėŗĢrŻ¼├┐«öFIFOųąīæ╚ļ4kx32biĢr«a╔·ųąöÓŻ¼ät“īäė│╠ą“Ą─ųąöÓŠĆ│╠į┌Ēææ¬ųąöÓĢrŻ¼├┐┤╬ų┴╔┘ūx16kBĪŻį┌ųąöÓĒææ¬ūx╚ĪFIFOöĄō■ĢrŻ¼▓╗ę¬ė├ŅÉ╦Ųė┌for(Ż╗Ż╗)Ą─▄ø╝■裣hīŹ¼FŻ¼▀@ĘN▓▀┬įį┌ė▓╝■Ģrą“╔Žī┘ė┌å╬┤╬įLå¢Ż¼ą¦┬╩Ą═Ž┬ĪŻų╗ėąDMA▓┼─▄ė|░l▀ē▌ŗįOėŗųąĄ─burstų▄Ų┌Ż¼ūŅ┤¾Ž▐Č╚└¹ė├ė▓╝■ąį─▄ĪŻį┌åóäėDMAĢrŻ¼ę╗Č©ę¬╩╣─▄╦³Ą─burst╬╗▓┘ū„ķLČ╚╣╠Č©×ķ16kBĪŻ▀@śėŻ¼├┐┤╬ųąöÓĒæ權═ūā│╔┴╦ŠSūoDMA«öŪ░īæ╚ļŠÅø_Ą─ųĖßśŻ¼╠Ņ╚ļ«öŪ░īæ╚ļŠÅø_ĄžųĘŻ¼╚╗║¾åóäėDMAĪŻ

į┌æ¬ė├│╠ą“ųąŻ¼╩╣ė├ę╗éĆČ©ĢrŠĆ│╠Ż¼═©▀^“īäė│╠ą“ūx╚ĪęĢŅlöĄō■Ż¼╚╗║¾Įø▀^ē║┐sŻ¼┤µĘ┼│╔JPEG2000Ė±╩ĮĄ─ęĢŅl╬─╝■ĪŻČ©Ģrūx╚ĪęĢŅlöĄō■Ą─╦ŃĘ©ąĶę¬▀Mąąā×╗»Ż¼ę“×ķ╚ń╣¹öĄō■ūx│÷ŠĆ│╠╠½┬²Ż¼ųąöÓŠĆ│╠īæ╚ļĢr┐╔─▄Ė▓╔w╬┤ūxū▀Ą─ŠÅø_Ż¼Ģ■įņ│╔┤µā”ęĢŅl│÷¼FüG╩¦öĄō■ļĄ─¼FŽ¾Ż¼ė░ĒæėøõøęĢŅlĄ─▀B└mąįĪŻ

5 ĮY╩°šZ

▒Š╬─▓╔ė├FPGA┼cŪČ╚ļ╩ĮCPU┤¾╚▌┴┐öĄō■┤µā”ŽÓĮY║ŽĄ─ĘĮ░ĖŻ¼į┌ŽĄĮyĖ„éĆ╠Ä└ĒŁh╣ØŠ∙│õĘų┐╝æ]ĄĮī”ęĢŅlöĄō■▓╔╝»ėøõøīŹĢrąį║═┐╔┐┐ąįĄ─ę¬Ū¾Ż¼įOėŗ┴╦ÖC▌dČÓ═©Ą└īŹĢręĢŅlöĄō■▓╔╝»ėøõøŽĄĮyĪŻŽĄĮyė▓╝■įOėŗ║åå╬Ż¼▓óŪę┐╔═¼Ģr▓╔╝»ČÓ┬ĘęĢŅlöĄō■ĪŻį┌─│ą═öĄūų╗»ī”┐╣ė¢ŠÜįu╣└ŽĄĮyųąĄ─æ¬ė├▒Ē├„Ż¼▒ŠįOėŗĘĮ░ĖØMūŃ┴╦ŅAŲ┌Ą─ųĖś╦ę¬Ū¾Ż¼ĮŌøQ┴╦▌dÖC╚╬䚎ĄĮyČÓ┬ĘęĢŅlöĄō■▓╔╝»┼cīŹĢrėøõøĄ─ĻPµIå¢Ņ}Ż¼į┌īŹĢręĢŅlą┼Žó▓╔╝»║═öĄō■ėøõøæ¬ė├ųąŠ▀ėą▌^║├Ą─═©ė├ąį║═öUš╣ąįĪŻ