š¬ę¬Ż║ĮķĮB┴╦ęįFPGA×ķų„┐žąŠŲ¼Ż¼ęį╣ŌÜ××ķ═©ėŹ├ĮĮķĄ─ęĢŅlą┼╠¢öĄūų═©ą┼īŹ“×čbų├Ą─įOėŗīŹ¼F▀^│╠Ż¼▓óī”ļŖ┬ĘĖ„éĆ─ŻēKĄ─╣”─▄╝░īŹ¼F╝ėęįšf├„ĪŻļŖ┬Ęį┌altium designerųąįOėŗ═Ļ│╔Ż¼▓╔ė├Ęų─ŻēK╩ĮĄ─įOėŗŻ¼╦╝┬Ęņ`╗ŅŻ¼ĮYśŗŪÕ╬·Ż¼ęūė┌īŹ¼FĪŻį┌Quartusó“ŁhŠ│Ž┬ė├VerilogHDLšZčį▀MąąŠÄ│╠▓óī”│╠ą“▀MąąĘ┬šµĪŻįōčbų├ęčū÷│╔┴╦īŹ╬’śė▒ŠŻ¼īŹ“×╩╣ė├▒Ē├„Ż║┐╔ęįīŹ¼FęĢŅlą┼╠¢Ą─é„▌öŻ¼▀_ĄĮįOėŗ╠ß│÷Ą─Į╠īWę¬Ū¾║═īŹļHą¦╣¹ĪŻ

╣Ō└węįŲõŅlĦīÆĪó╚▌┴┐┤¾Īó╦ź£pąĪĄ╚ā׳cĮo═©ą┼ŅIė“ĦüĒĄ─Ė─Ė’║═äōą┬Ż¼ą╬│╔┴╦ę╗éĆą┬┼d«aśIĪŻöĄūų═©ą┼ī”▒╚é„ĮyĄ──ŻöM═©ą┼ėą┐╣Ė╔ö_─▄┴”ÅŖĪó▀mė├ĘČć·ÅVĪó▒Ż├▄ąį─▄ÅŖĪóęūė┌╝»│╔Īó╣”─▄ĘĆČ©Ą╚ā׳cĪŻöĄūų╣Ō└w═©ą┼╝µėąā╔š▀Ą─ā׳cŻ¼▒žīó│╔×ķ═©ą┼ŅIė“Ą─░lš╣ĘĮŽ“ĪŻ

ęĢŅlą┼╠¢Ą─╣Ō└wé„▌öėąīŹĢrĪó£╩┤_ĪóŪÕ╬·Ą─ā׳cĪŻį┌īŹ“×ŅIė“Ż¼┐╔ęį┐ņ╦┘£╩┤_Ąžé„▀fīŹ“׳DŽ±Ż¼ĮoīŹ“ך▀Ė³┐╔┐┐Ą─ą┼ŽóĪŻį┌▒O┐žĘĮ├µŻ¼┐╔ęįīŹĢré„▀f▒O┐žłDŽ±Ż¼╝┤╣Ø╝s│╔▒ŠŻ¼ėųėąĖ▀Ą─é„▌ö┘|┴┐ĪŻę“┤╦Ż¼ęĢŅlą┼╠¢Ą─╣Ō└wé„▌öĄ─蹊┐┼cīŹ¼FŻ¼īóĘĮ▒Ń╚╦éāĄ─īW┴ĢĪó╣żū„║═╔·╗ŅĪŻ

▒Š╬─╩Ūßśī”Ųš═©╣ż┐ŲŅÉĖ▀ąŻųąŻ¼ĘŪ═©ą┼┼cą┼Žó╣ż│╠īŻśIĄ╚īW┐ŲŻ¼Š▀ėąŲš╝░ąįīŹ“×Į╠īW┐Ų─┐╦∙čąųŲĄ─äōą┬īŹ“×Į╠īWāxŲ„ĪŻįōīŹ“×āxŲ„Ą─═Ų│÷Ż¼ėą└¹ė┌Ä═ų·Ė▀Ą╚īWąŻ╗∙ĄAąįīW┐ŲīŹ“ךn│╠Ą─╠ß╔²Ż¼žSĖ╗┼c═Ļ╔ŲīŹ“ךnā╚╚▌Ż¼╩╣īW╔·┴╦ĮŌ¼F┤·╝╝ągĄ─░lš╣┼cŽÓĻPų¬ūRĄ─šŲ╬šĪŻ

1 ŽĄĮyĄ─ė▓╝■ĮYśŗ

š¹╠ūčbų├ė╔ā╔┤¾▓┐ĘųĮM│╔Ż║╣ŌĮė╩šŲ„║═╣Ō░l╔õŲ„ĪŻā╔š▀ų«ķgęį╣Ō└w▀BĮėĪŻ╣Ō░l╔õŲ„┼c╣ŌĮė╩šć╠Ą─╣żū„įŁ└ĒŽÓ╗źĻP┬ōŻ¼ę╗éĆ╩Ū┴Ēę╗éĆĄ──µ▀^│╠Ż╗╣Ō░l╔õŲ„╩ŪīóęĢŅlĄ─ļŖą┼╠¢▐Dūā│╔╣Ōą┼╠¢Ż¼╣ŌĮė╩šŲ„╩Ūīó╣Ōą┼╠¢▐Dūā│╔ęĢŅlĄ─ļŖą┼╠¢ĪŻ

╣Ō░l╔õŲ„ė╔×V▓©Ę┼┤¾ĪóA/D▐DōQĪó┐žųŲ▓┐ĘųĪó▓ó/┤«▐DōQĪóļŖ/╣Ō─ŻēK▓┐ĘųĮM│╔ĪŻ

╣ŌĮė╩šŲ„ė╔╣Ō/ļŖ▐DōQ▓┐ĘųĪó┤«/▓ó▐DōQĪó┐žųŲ▓┐ĘųĪóD/A▐DōQĪó─ŻöMą┼╠¢Ę┼┤¾▓┐ĘųĮM│╔ĪŻ

2 ŽĄĮyļŖ┬ĘįOėŗ

2.1 ļŖį┤

š¹╠ūčbų├āHęį7.5 Vų▒┴„ļŖį┤╣®ļŖŻ¼ā╚▓┐╝»│╔ļŖ┬ĘąĶė├ĄĮ5VĪó1.5VĪó3.3VĄ─ļŖį┤ĪŻ5VļŖį┤ė╔L7805╚²æBĘĆē║ļŖį┤╠ß╣®Ż¼3.3V║═1.5VĘųäeė╔ASM117-3.3║═ASM117-1.5╠ß╣®ĪŻ

2. 2 FPGAų„┐ž▓┐Ęų

ļŖ┬Ę▓╔ė├ą═╠¢×ķEPIC3144C8Ą─FPGA×ķų„┐žąŠŲ¼Ż¼ė╔32 MHzĄ─Š¦š±╠ß╣®╣żū„ĢrńŖĪŻąŠŲ¼╣▓ėą4éĆĢrńŖ▌ö╚ļČ╦Ż¼▀xŲõę╗▌ö╚ļŠ¦š±ĢrńŖĪŻė╔ė┌FPGAĖ„éĆ─ŻēKČ╝ė├ĄĮŻ¼╦∙ęįĖ„éĆ─ŻēKČ╝ąĶę¬╣®ļŖ║═ĮėĄžĪŻ

FPGAā╚▓┐ėąā╔éƵiŽÓŁhŻ¼┐╔ęį▀MąąĘųŅl║═▒ČŅlŻ¼ęįĄ├ĄĮ▓╗═¼Ą─Ņl┬╩ĪŻ░l╔õŲ„ųąFPGA╠ß╣®─ŻöĄ▐DōQąŠŲ¼║═▓ó/┤«▐DōQąŠŲ¼Ą─ĢrńŖ▓óīó─ŻöĄ▐DōQŲ„▌ö│÷Ą─░╦╬╗öĄō■ŠÄ┤a│╔╩«╬╗öĄō■é„╦═Įo▓ó┤«▐DōQąŠŲ¼Ż¼╝┤═Ļ│╔8B10BŠÄ┤a║═öĄō■é„▌öĪŻĮė╩šŲ„ųąFPGA╠ß╣®öĄ─Ż▐DōQŲ„╣żū„ĢrńŖ║═┤«▓ó▐DōQŲ„Ą─ģó┐╝ĢrńŖŻ¼▓óīó┤«▓ó▐DōQŲ„▌ö│÷Ą─╩«╬╗öĄō■ĮŌ┤aŻ¼▀ĆįŁ×ķ░╦╬╗öĄō■é„▌öĮoöĄ─Ż▐DōQŲ„ĪŻFPGAĄ─╣”─▄ė╔VerilogŠÄ│╠īŹ¼FŻ¼│╠ą“▓╔ė├AS(ų„äė)┼õų├ĘĮ╩ĮŽ┬▌dĄĮFPGA

2.3 ęĢŅlą┼╠¢Ą─╠Ä└Ē╝░▓╔╝»

ęĢŅlą┼╠¢Įø×V▓©ĪóĘ┼┤¾Īó═¼▓ĮĘųļxŻ¼ė╔─ŻöĄ▐DōQ╝»│╔ąŠŲ¼▓╔╝»▐DōQ│╔öĄūųą┼╠¢ĪŻ

2.3.1 ×V▓©Ę┼┤¾▓┐Ęų

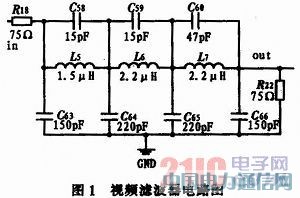

į┌ī”ęĢŅlą┼╠¢▀Mąą▓╔śėĢrŻ¼«öą┼╠¢ųą║¼ėą┤¾ė┌Č■Ęųų«ę╗Ą─▓╔śėŅl┬╩Ż¼╚ń╣¹▓╔śėŅl┬╩▓╗ē“Ė▀Ż¼Š═Ģ■«a╔·╗ņ»Bą┼╠¢ĪŻ╗ņ»Bą┼╠¢▓╗─▄ė├öĄūų×V▓©ĘĮĘ©│²╚źŻ¼ąĶę¬ė├ė▓╝■×V▓©ĪŻA/D▐DōQĄ─▓╔śėŅl┬╩ąĶę¬Ė▀ė┌ęĢŅlą┼╠¢ūŅĖ▀Ņl┬╩Ą─2Ī½10▒ČŻ¼×ķ┴╦į┌─ŻöĄ▐DōQļAČ╬▓╗│÷¼FĖ³Ė▀Ņl┬╩Ż¼╝┤▓╗│÷¼F╗ņ»BĖ╔ö_ą┼╠¢Ż¼×V▓©ąĶį┌A/D▐DōQų«Ū░▀MąąĪŻĖ∙ō■╦∙ąĶęĢŅlą┼╠¢Ą─ĦīÆęį╝░┐╣╗ņ»B×V▓©╦∙ąĶꬥ─╠žąįŻ¼įOėŗę╗éĆ7╝ēĄ─Ą══©×V▓©Ų„Ż¼Įžų╣Ņl┬╩×ķ6 MHzŻ¼ļŖ┬Ę╚ńłD1╦∙╩ŠĪŻ

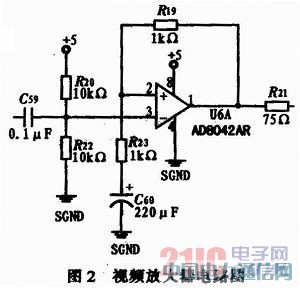

Ę┼┤¾ļŖ┬Ę▓╔ė├├└ć°─ŻöMŲ„╝■╣½╦Š│÷ŲĘĄ─╝»│╔AD8042üĒīŹ¼FĪŻAD8042╩Ūę╗┐Ņ╣”║─Ą═ĪóļŖē║Ę┤üą═Ą─Ė▀╦┘Ę┼┤¾Ų„ĪŻ╦³Š▀ėąå╬ļŖį┤╣®ļŖ─▄┴”Ż¼Ųõ0.1BDį÷ęµŲĮ╠╣Č╚×ķ14 MHzŻ¼▓╔ė├5 VļŖį┤ĢrĄ─▓ŅĘųį÷ęµ║═ŽÓ╬╗š`▓ŅĘųäe×ķ0.04Żź║═0.06ŻźĪŻ╣żū„ė┌5 VļŖį┤ĢrŻ¼╦³Š▀ėą160 MHzĄ─ĦīÆĪŻĄ═╩¦šµ║═┐ņ╦┘Į©┴ó╠žąį╩╣Ą├╦³┐╔ęįė├ė┌ŠÅø_å╬ļŖį┤║═Ė▀╦┘öĄ─Ż▐DōQļŖ┬ĘŻ¼ļŖ┬Ę╚ńłD2╦∙╩ŠĪŻ

łDųąAD8042▓╔ė├5 VļŖį┤╣®ļŖŻ¼▓╔ė├ę╗╝ēĘ┼┤¾ĪŻ

2.3.2 ═¼▓ĮĘųļx▓┐Ęų

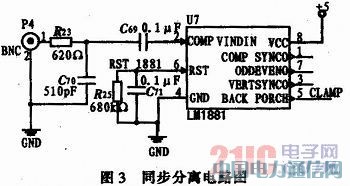

╚½ļŖęĢą┼╠¢ųą│²┴╦łDŽ±ą┼╠¢═ŌŻ¼▀Ć░³║¼Å═║Ž═¼▓Įą┼╠¢Ż║ė╔ąąĪół÷║═╔½Ė▒▌d▓©Ą╚ĮM│╔Ż╗▀@ą®═¼▓Įą┼╠¢┼cłDŽ¾Īó┬Ģ궹┼╠¢░┤ššę╗Č©ęÄĖ±Ą─ć°ļHųŲ╩ĮŠÄųŲś╦£╩śŗ│╔Ż¼╩╣Ą├š¹éĆęĢŅlą┼╠¢═Ļš¹ģfš{Įyę╗ĪŻ╦∙ęįį┌▀Mąąé„▌ö╠Ä└ĒęĢŅlą┼╠¢ĢrŻ¼ę¬ī”ŲõųąĄ─═¼▓Įą┼╠¢īŹ╩®╝╝ągĘųļxŻ¼ęį▒ŃŽÓæ¬┐žųŲ╠Ä└ĒŻ¼Š▀¾wļŖ┬Ę▓╔ė├LM1881╝»│╔ąŠŲ¼īŹ¼FĪŻįōąŠŲ¼┐╔Å─╚½ļŖęĢą┼╠¢ųą╠ß╚Ī┼cĘųļx│÷Ż║ąą║═ł÷Īó║¾čė═¼▓ĮĪóŲµ┼╝ł÷Ą─łDŽ±ą┼ŽóĪŻłDŽ±Ą─Å═║ŽęĢŅlą┼╠¢ų▒Įėė╔ŽĄĮyĄ─ŽÓĻPįOéõ╠ß╣®Ż¼ąŠŲ¼Ą─BACK PORCH╣▄─_į┌ęĢŅlą┼╠¢Ž¹ļ[Ų┌ķg«a╔·║¾čė├}ø_Ż¼įō─_ĮėĄĮA/D▐DōQŲ„AD9280Ą─CLAMPČ╦┐┌╝┤19─_Ż¼╩╣A/D▐DōQŲ„į┌ą┼╠¢Ą─Ž¹ļ[Ų┌ķg╠Äė┌ŃQ╬╗╣żū„─Ż╩ĮŻ¼┐╔īóŽ¹ļ[ļŖŲĮŃQ╬╗į┌0ļŖŲĮĄ─╬╗ų├Ż¼Å─Č°╩╣Ą├▓╔╝»╠Ä└Ēą┼╠¢Ģr─▄ē“š²┤_Ą├░č╬šĖ„éĆą┼╠¢ķgĄ─Ģrą“ĻPŽĄ║═▀ē▌ŗĻPŽĄŻ¼═Ļ│╔═¼▓Įą┼╠¢ĘųļxĄ─╣”─▄ĪŻ

ĘųļxļŖ┬Ę▓╔ė├├└ć°ć°╝ę░ļī¦¾wŲ„╝■╣½╦Š│÷ŲĘĄ─╝»│╔LM1881üĒīŹ¼FŻ¼ļŖ┬Ę╚ńłD3╦∙╩ŠĪŻ

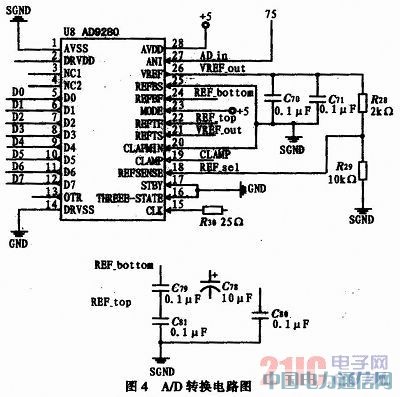

2.3.3 A/D▐DōQ▓┐Ęų

─ŻöĄ▐DōQļŖ┬Ę═¼śė▓╔ė├├└ć°─ŻöMŲ„╝■╣½╦Š│÷ŲĘĄ─╝»│╔AD9280üĒīŹ¼FŻ¼Ųõ╣żū„ĢrńŖŅl┬╩įOČ©×ķ32MHZŻ¼ė╔FPGA╠ß╣®ĪŻą┼╠¢ė╔AIN╣▄─_▌ö╚ļŻ¼D0Ī½D7▌ö│÷▐DōQ║¾Ą─8╬╗Č■▀MųŲöĄō■ĪŻSTBY║═THREE-STATE─_ĮėĄžŻ¼ęį▒ŻūCąŠŲ¼š²│Ż╣żū„ĪŻCLAPMINĮėĄžŻ¼░čŽ¹ļ[ļŖŲĮŃQ╬╗×ķ0ļŖŲĮŻ¼ŲõļŖ┬Ę╚ńłD4╦∙╩ŠĪŻ

2.4 ą┼╠¢░l╦═▓┐Ęų

ė╔FPGA╠Ä└Ē║¾Ą─öĄō■ę¬═©▀^╣Ō└w░l╦═Ż¼▓╗ąĶŽ╚īó▓óąąöĄō■▐DōQ×ķ┤«ąąöĄō■Ż¼į┘īó┤«ąąöĄō■▐DōQ×ķ╣Ōą┼╠¢ĪŻ

2.4.1 ▓ó/┤«▐DōQ

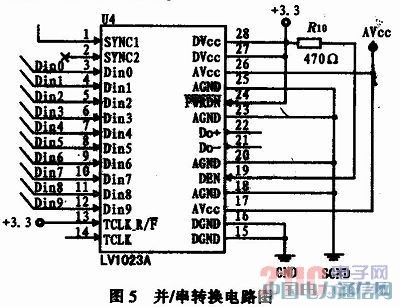

ļŖ┬Ę▓╔ė├┤«╗»Ų„DS92LV1023╝»│╔ąŠŲ¼īŹ¼FŻ¼ļŖ┬Ę╚ńłD5╦∙╩ŠŻ¼Ųõī”æ¬Įė╩šČ╦ė╔ĮŌ┤«Ų„DS92LV1224╝»│╔ąŠŲ¼═Ļ│╔ĪŻDS92LV1023┐╔ęįīó10╬╗▓óąąöĄō■▐DōQ×ķ┤«ąą▓ŅĘųöĄō■┴„Ż¼įō▓ŅĘųöĄō■┴„┐╔ęįė╔DS92LV1224▀ĆįŁ×ķ10╬╗Ą─▓óąąöĄō■ĪŻ▀@ę╗ĮMąŠŲ¼ā╚▓┐ėąµiŽÓŁhŻ¼┐╔ęį×ķöĄō■▌ö│÷ūį╝║Ųź┼õĢrńŖĪŻ┤«╗»Ų„LV1023ģó┐╝ĢrńŖ▀x×ķ32MHzŻ¼öĄō■į┌įōĢrńŖŅl┬╩Ž┬▌ö╚ļŻ¼ŲõąŠŲ¼ā╚▓┐Ųź┼õ«a╔·öĄō■▌ö│÷ĢrńŖŻ¼├┐ę╗éĆ10╬╗▓óąąöĄō■▐DōQ×ķ12╬╗┤«ąąöĄō■Ż¼ŲõųąČÓ│÷ę╗éĆŲ╩╝╬╗║═ę╗éĆĮKų╣╬╗Ż¼╦∙ęįėąą¦Ņl┬╩×ķ320 MĪŻĮŌ┤«Ų„Ą─ģó┐╝ĢrńŖČ©×ķ16MHzŻ¼ęįØMūŃöĄō■é„▌öąĶŪ¾ĪŻ

ė╔ė┌ęĢŅlą┼╠¢╩ŪīŹĢr▓╗öÓĄ─Ż¼╦∙«a╔·Ą─öĄō■┴„▀B└m▀MąąŻ¼╦∙ęįļŖ┬Ę▓╗─▄įOų├▀M╚ļĖ▀ūĶæB╗“╩ĪļŖ─Ż╩ĮŻ¼ę“┤╦LV1023Ą─DEN║═PWRDNČ╝ų├Ė▀ļŖ╬╗ĪŻ

┤«ąąöĄō■Ą─£╩┤_é„▌öąĶ═ū┤«╗»Ų„║═ĮŌ┤«Ų„═¼▓ĮŻ¼įōĮMąŠŲ¼ėą2ĘN═¼▓ĮĘĮ╩ĮŻ║

1)┐ņ╦┘═¼▓Į ┤«╗»Ų„LV1023░l╦═ę╗ĮM═¼▓Įą┼╠¢Ż¼ė╔▀B└m╩Ū6éĆ“1”║═6éĆ“0”ĮM│╔Ż¼░l╦══¼▓Įą┼╠¢╩Ūė╔SYNC1║═SYNC2┐žųŲĄ─Ż¼«öSYNC1╗“SYNC2ų├Ė▀ļŖŲĮ│ų└mĢrķg│¼▀^6éĆĢrńŖų▄Ų┌ĢrŻ¼ätķ_╩╝▀B└m░l╦══¼▓Įą┼╠¢Ż¼«öĮŌ┤«Ų„LV1224Įė╩šĄĮ═¼▓Įą┼╠¢║¾▒Ńķ_╩╝įćłDµiČ©ĢrńŖą┼╠¢Ż¼µiČ©═Ļ│╔ų«Ū░LOCK▒Ż│ųĖ▀ļŖŲĮŻ¼µiČ©═Ļ│╔║¾LOCK╠°ūā×ķĄ═ļŖŲĮĪŻ

2)ļSÖC═¼▓ĮĘĮ╩Į įōĮMąŠŲ¼į┌ø]ėą═¼▓Įą┼╠¢é„▌öĄ─ŪķørŽ┬╚į╚╗┐╔ęį═Ļ│╔µiČ©Ż¼▀@╩╣įōĮMąŠŲ¼į┌ķ_Ę┼ł÷║ŽĄ├ĄĮæ¬ė├ĪŻļSÖC═¼▓ĮĢrŻ¼┤«╗»Ų„▓╗░l╦══¼▓Įą┼╠¢Ż¼ĮŌ┤«Ų„ų▒Įėī”▓ŅĘųöĄō■┴„▀MąąµiČ©Ż¼įōµiČ©ĘĮ╩ĮĢ■╩▄ĄĮ│§╩╝ĢröĄō■║═ĢrńŖĄ─ŽÓ╬╗ė░ĒæŻ¼ę▓Ģ■╩▄ĄĮöĄō■▒Š╔ĒĄ─ė░ĒæŻ¼«öę╗éĆ╠ž╩ŌĄ─öĄō■łDśėĘ┤Å═│÷¼FĢrŻ¼ĮŌ┤«Ų„┐╔─▄│÷¼FµiČ©Õeš`Ż¼ĘQ×ķRMTĪŻĄ½«ö═¼▓ĮüG╩¦║¾Ż¼ĮŌ┤«Ų„Ģ■ųžą┬µiČ©ĢrńŖŻ¼╗ųÅ══¼▓ĮĪŻ

ė╔ė┌įōļŖ┬Ę▓╔ė├ļSÖC═¼▓ĮĘĮ╩ĮĪŻ┤«╗»Ų„Ą─SYNC1║═SYNC2æę┐šĪŻ

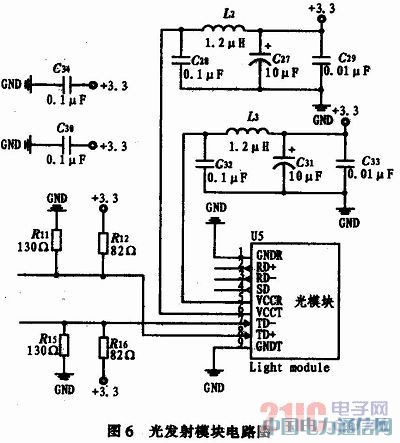

2. 4. 2 ļŖ/╣Ō─ŻēK

▓╔ė├ą═╠¢×ķHNMS-XEMC41XSC20Ż¼╣żū„▓©ķLį┌T1310nm/R1550nmĄ─å╬└wļpŽ“ę╗¾w╗»╩š░l─ŻēKŻ¼īóļŖą┼╠¢▓ŅĘųöĄō■┴„▐D│╔╣ŌöĄō■ą┼╠¢┴„Ż¼ļŖ┬Ę╚ńłD6╦∙╩ŠĪŻ

2.5 ą┼╠¢Ą─Įė╩š╝░╠Ä└Ē

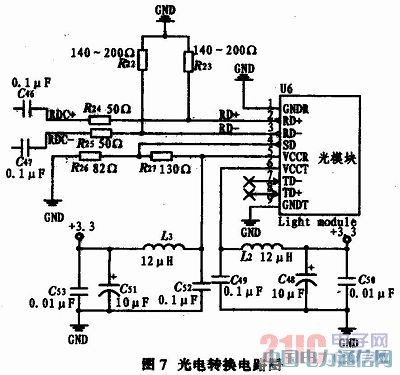

2.5.1 ╣Ō/ļŖ▐DōQ─ŻēK

čbų├ęįå╬└w▀Mąąą┼╠¢é„▌öŻ¼╣Ōą┼╠¢é„▌öĄĮĮė╩ščbų├║¾Ż¼ąĶę¬▀ĆįŁ×ķļŖą┼╠¢Ż¼╝┤▓ŅĘųļŖē║öĄō■┴„ĪŻ▓╔ė├ą═╠¢×ķHNMS-XEMC41XSC20Ż¼╣żū„▓©ķLį┌T1310 nm/R1550 nmĄ─å╬└wļpŽ“ę╗¾w╗»╩š░l─ŻēKŻ¼īó╣Ōą┼╠¢▐DōQ×ķļŖą┼╠¢ĪŻ▐DōQ║¾Ą─▓ŅĘųą┼╠¢ė╔RD+║═RD-▌ö│÷ĪŻļŖ┬Ę╚ńłD7╦∙╩ŠĪŻ

2. 5. 2 ┤«▓ó▐DōQ

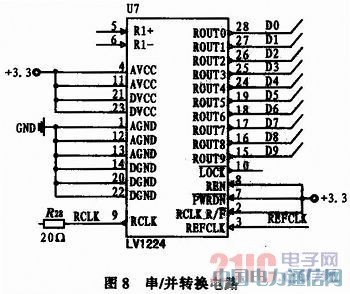

čbų├▓╔ė├┼c░l╦═Ų„ųąĄ─┤«╗»Ų„DS92LV1023ŽÓŲź┼õĄ─ĮŌ┤«Ų„DS92LV1224ĪŻ░l╦═Ų„ųąĄ─┤«╗»Ų„īó10╬╗Ą─▓óąąöĄō■▐DōQ×ķ┤«ąąĄ─▓ŅĘųöĄō■┴„Ż¼ę“┤╦į┌Įė╩šŲ„ųąąĶė├ŽÓæ¬Ą─ĮŌ┤«Ų„īó┤«ąą▓ŅĘųöĄō■┴„▀ĆįŁ×ķ▓óąąöĄō■ĪŻ

DS92LV1224ā╚▓┐ėąµiŽÓŁhŻ¼į┌Įė╩šöĄō■┴„Ģr┐╔ęįĖ∙ō■öĄō■Ą─Ņl┬╩ūįąąŲź┼õĮė╩šĢrńŖŻ¼═ŌĮńų╗ąĶ×ķŲõ╠ß╣®ģó┐╝ĢrńŖĪŻ┤╦╠Äģó┐╝ĢrńŖ▀x×ķ16MHzŻ¼ė╔FPGA┐žųŲ▓┐Ęų╠ß╣®ĪŻąŠŲ¼▀ĆŲź┼õ┴╦┼cĮŌ┤«║¾Ą─öĄō■═¼▓ĮĄ─ĢrńŖŻ¼ęįų·ė┌▐DōQ║¾Ą─▓óąąöĄō■▌ö│÷ĪŻģó┐╝ĢrńŖ║═öĄō■▌ö│÷ĢrńŖĘųäe×ķREFCLK║═RCLKę²─_ĪŻ×ķ┴╦▒ŻūCęĢŅlą┼╠¢Ą─▀B└mąį║═īŹĢrąįŻ¼ąĶ▒▄├ŌąŠŲ¼╠Äė┌╩ĪļŖ─Ż╩Į╗“Ė▀ūĶ─Ż╩ĮĪŻę“┤╦PWRDN║═RENąĶĮėĖ▀ļŖŲĮĪŻRCLK-R/FĮėĖ▀ļŖŲĮŻ¼╝┤▀xō±ĢrńŖ╔Ž╔²čž▌ö│÷öĄō■ĪŻ

įōĮMąŠŲ¼ėą2ĘN═¼▓ĮĘĮ╩ĮŻ║┐ņ╦┘═¼▓Į║═ļSÖC═¼▓ĮĪŻ┐ņ╦┘═¼▓Į╩Ūė╔┤«╗»Ų„░l╦═ę╗ĮMė╔▀B└mĄ─6éĆ“1”║═“0”ĮM│╔Ą─═¼▓Įą┼╠¢Ż¼ĮŌ┤«Ų„╩šĄĮą┼╠¢║¾µiČ©öĄō■ĢrńŖŻ¼µiČ©═Ļ│╔ų«Ū░LOCK▒Ż│ųĖ▀ļŖŲĮŻ¼═¼▓Į═Ļ│╔║¾╠°ūā×ķĄ═ļŖŲĮĪŻ═¼▓Įą┼╠¢Ą─░l╦═╩Ūė╔┤«╗»Ų„Ą─SYNC1║═SYNC2┐žųŲĄ─Ż¼ų╗ę¬ā╔š▀ų«ę╗ų├Ė▀ļŖŲĮ│ų└mĢrķg│¼▀^6éĆĢrńŖų▄Ų┌Ż¼┤«╗»Ų„Š═ķ_╩╝▀B└m░l╦══¼▓Įą┼╠¢ĪŻ┐ņ╦┘═¼▓ĮŠ▀ėą┐ņ╦┘£╩┤_Ą─ā׳cŻ¼Ą½į┌ķLŠÓļxĄ─ą┼╠¢é„▌öųąŻ¼╣Ō└wų╗é„▀föĄō■Ż¼¤oĘ©║▄║├Ą─é„▀f┤«╗»Ų„║═ĮŌ┤«Ų„Ą─SYNC║═LOCKą┼╠¢ĪŻę“┤╦▓╔ė├ļSÖC═¼▓ĮĘĮ╩ĮĪŻļSÖC═¼▓ĮĘĮ╩Į┤«╗»Ų„▓╗ąĶ░l╦══¼▓Įą┼╠¢Ż¼ĮŌ┤«Ų„ų▒Įėī”öĄō■┴„▀MąąµiČ©Ż¼īŹ¼F═¼▓ĮŻ¼µiČ©üG╩¦║¾Ż¼ĮŌ┤«Ų„Ģ■ųžą┬µiČ©ĢrńŖĪŻīóLOCKĮėĄĮFPGAęį▀MąąīŹĢr┐žųŲĪŻ┤«/▓ó▐DōQļŖ┬Ę╚ńłD8╦∙╩ŠĪŻ

2.6 D/A▐DōQ╝░ęĢŅlą┼╠¢▌ö│÷

2.6.1 D/A▐DōQ▓┐Ęų

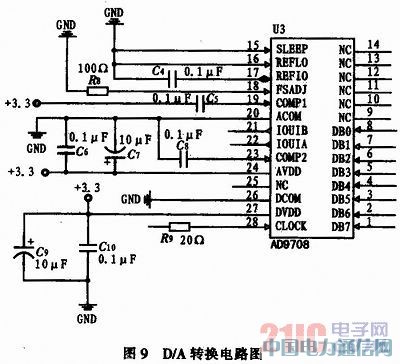

▓╔ė├├└ć°─ŻöMŲ„╝■╣½╦Š│÷ŲĘĄ─AD9708Ż¼╦³ī┘ė┌Ė▀ąį─▄ĪóĄ═╣”║─CMOSöĄ─Ż▐DōQŲ„Ż¼─▄╠ß╣®│÷╔½Ą─Į╗┴„║═ų▒┴„ąį─▄Ż¼ų¦│ųūŅĖ▀125 Mz/sĄ─Ė³ą┬╦┘┬╩ĪŻ╣żū„ĢrńŖįO×ķ16 MHzŻ¼ė╔FPGA╠ß╣®ĪŻ

AD9708Ą─═Ōć·ļŖ┬Ę╚ńłD9╦∙╩ŠĪŻŲõųąREFLO╩Ū▐DōQ╗∙£╩Ą─ģó┐╝ĄžŻ¼┤╦─_ĮėĄžĮ¹ė├ā╚▓┐ģó┐╝ļŖē║ĪŻCOMP1╩Ūįļ┬Ģ╦ź£p─Ż╩ĮįOų├Č╦Ż¼┤╦╠Ä┤«Įė0.1 μFĄ─ļŖ╚▌─▄▀_ĄĮ▌^║├Ą─▐DōQą¦╣¹ĪŻR9╩ŪĮKČ╦Ųź┼õļŖūĶęįŽ¹│²Ė▀Ņlš±╩ÄĪŻC9║═C10ė├ęį×V│²öĄūųļŖį┤╝y▓©Ż¼C6ĪóC7ė├ęį×V│²─ŻöMļŖį┤╝y▓©ĪŻ▓óąąöĄō■ė╔DB0Ī½DB7▌ö╚ļŻ¼▐DōQ║¾Ą─öĄō■ė╔IOUTA▌ö│÷ĪŻ┤╦╠Ä▌ö│÷Ą─ą┼╠¢ĒÜĮø▀\Ę┼Ę┼┤¾║¾Ż¼▓┼─▄ØMūŃ═©ė├ąįęĢŅl’@╩ŠŲ„Ą─╝╝ągę¬Ū¾ĪŻ

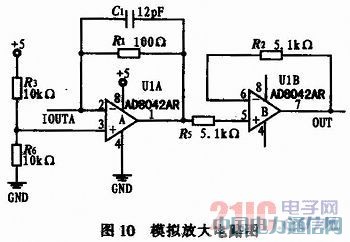

2.6.2 ─ŻöMĘ┼┤¾╝░ęĢŅlą┼╠¢▌ö│÷

▓╔ė├AD8042īŹ¼Fą┼╠¢Ą─Ę┼┤¾Ż¼╚ńłD10╦∙╩ŠĪŻULAīóAD9708▌ö│÷Ą─ļŖ┴„ą┼╠¢▐DōQ×ķļŖē║ą┼╠¢Ż¼ŲõųąC1ų„ę¬ū„ė├╩Ū╚ź│²Ė▀ŅlĖ╔ö_ĪŻULBū„×ķļŖē║Ė·ļSŲ„Ż¼ė├ė┌ūĶ┐╣Ųź┼õĪŻę¬Ū¾Ą─▌ö│÷ūĶ┐╣╩Ū75 ΩŻ¼ļŖē║Ė·ļSŲ„╩╣▌ö│÷ūĶ┐╣×ķ0Ż¼į┘┤«┬ōę╗éĆ75 Ω(į┌ULBĄ─7─_ų«║¾Ż¼łDųą╬┤ś╦│÷)Ż¼üĒØMūŃŲź┼õę¬Ū¾ĪŻ

3 │╠ą“įOėŗ╝░Ę┬šµ

ŽĄĮy▓╔ė├VerilogHDLšZčį▀Mąą│╠ą“ŠÄīæŻ¼į┌Quartusó“ŁhŠ│Ž┬ŠÄ▌ŗĘ┬šµĪŻFPGAā╚▓┐ĢrńŖė╔32 MHzŠ¦š±╠ß╣®ĪŻFPGAĄ─╣żū„╩ŪŻ║1)╠ß╣®D/A▐DōQąŠŲ¼AD9708ĪóA/D▐DōQąŠŲ¼AD9280Īó▓ó┤«▐DōQąŠŲ¼LV1023Ą─╣żū„ĢrńŖ║═┤«▓ó▐DōQąŠŲ¼LV1224Ą─ģó┐╝ĢrńŖŻ¼Č╝╩Ū16 MHzŻ╗2)░l╦═Č╦ī”öĄō■▀Mąą8B10BŠÄ┤aŻ¼▓óīó▐DōQ║¾Ą─öĄō■é„╦═Įo┤«╗»Ų„Ż╗Įė╩šČ╦½@╚Ī┤«▓ó▐DōQ║¾Ą─╩«╬╗öĄō■Ż¼▀MąąĮŌ┤aŻ¼▀ĆįŁ×ķŠÄ┤aŪ░Ą─░╦╬╗öĄō■Ż¼▓óīóĮŌ┤a║¾Ą─öĄō■é„╦═ĮoöĄ─Ż▐DōQąŠŲ¼ĪŻ

3.1 8B10BŠÄĮŌ┤a

8B10BŠÄ┤a╩Ū─┐Ū░Ė▀╦┘┤«ąą═©ėŹŲš▒ķ▓╔ė├Ą─ŠÄ┤aĘĮ╩ĮŻ¼8B10BŠÄ┤aĄ──┐Ą─╩Ūīó░╦╬╗öĄō■▐DōQ│╔10╬╗Ą─öĄō■Ż¼▓ó╩╣▐DōQ║¾Ą─öĄō■┴„ųą“0”║═“1”Ą─öĄ┴┐ŲĮ║ŌŻ¼▒▄├Ō░l╦═▀^│╠ųąę“▀^ČÓųžÅ═Ą─│÷¼F“0”╗““1”Č°░l╔·Ą─Õeš`Ż¼╠ßĖ▀ŠĆ┬Ęé„▌öĄ─ąį─▄Ż¼ėą└¹ė┌Įė╩šŲ„Ė³£╩┤_Ą─▓ČūĮ═¼▓ĮĢrńŖŻ¼Č°Ūę▓╔ė├╠žČ©Ą─┤aį¬┐╔ęį╩╣Įė╩▄Č╦Ė³£╩┤_Ąžī”£╩┤aį¬ĪŻ

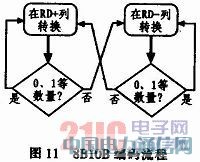

8B10BŠÄ┤a┐╔ęį┐┤│╔╩Ū5B6B║═3B4BŠÄ┤aĄ─ĮM║ŽŻ¼ĮM║Ž▀^║¾ėąą®ŠÄ┤a┐╔─▄ėąā╔éĆųĄŻ¼“1”║═“0”Ą─▓ŅųĄĘQ×ķŲĮ║ŌČ╚Ż¼ė├RD-▒Ē╩ŠŲĮ║ŌČ╚×ķ+2╗“0Ż¼RD+▒Ē╩ŠŲĮ║ŌČ╚-2╗“0ĪŻīó▐DōQ║¾Ą─öĄō■ĮėŲĮ║ŌČ╚Ęų×ķRD-║═RD+ā╔┴ąĪŻįOūā┴┐DISPIN▒Ē╩Šš²į┌▐DōQĄ─öĄĄ─ŲĮ║ŌČ╚Ż¼DISPOUT▒Ē╩ŠŽ┬ę╗éĆ▐DōQĄ─öĄĄ─ŲĮ║ŌČ╚ĪŻ│§╩╝ĢrįODISPIN┼cDISPOUTŽÓĄ╚Ż¼Ž╚Å─RD-ųąķ_╩╝▐DōQŻ¼╚ń╣¹▐DōQ║¾Ą─öĄ“0”║═“1”Ą─öĄ┴┐ŽÓĄ╚Ż¼└^└mį┌RD-┴ąųą▐DōQŽ┬ę╗éĆöĄŻ¼╚ń╣¹“0”║═“1”Ą─öĄ▓╗Ą╚Ż¼ät▐DĄĮRD+┴ąųą▐DōQĪŻ═¼└Ēį┌RD+┴ąųąŻ¼╚ń╣¹“0”Īó“1”éĆöĄŽÓĄ╚ät└^└mį┌RD+ųąŻ¼Ę±ätōQĄĮRD-ųąĪŻ

ĮŌ┤a▓┐Ęųīó10╬╗öĄō■Ą─Ū░┴∙╬╗║═║¾╦─╬╗Ęųäe░┤šš5B6B║═3B4BĄ─┴ą▒ĒĮŌ┤a╝┤┐╔ĪŻ

3.2 Ę┬šµ

įOėŗ│╠ą“ĮøQuartusó“ŠC║ŽŲ„ŠÄūgŠC║Ž│╔╣”║¾Ż¼┐╔ęįī”▌ö╚ļöĄō■Īóųąķg«a╔·Ą─öĄō■Īó▌ö│÷öĄō■▀MąąĘ┬šµĪŻčbų├▓╔ė├Ą─8B10BŠÄ┤aĘĮ╩ĮŻ¼Ęų×ķ3B4B║═5B6B▀MąąŠÄ┤aĪŻĮŌ┤a▓┐Ęųę└ššŠÄ┤aĢrŽÓ═¼Ą─Ęų░līó╩«╬╗öĄō■Ęų×ķ4B║═6BĘųäeĮŌ┤aĪŻĮŌ┤a║¾į┘░┤Ēśą“ĮM║Ž│╔8╬╗öĄō■ĪŻ│╠ą“ęį4B3BĪó6B5BĘųäe▓ķ▒ĒĄ─ĘĮ╩ĮīŹ¼FĪŻ

│╠ą“Ę┬šµłD╚ńłD12╦∙╩ŠŻ¼adin╩ŪŠÄ┤aų«Ū░Ą─░╦╬╗öĄō■Ż¼įO×ķų┤╬╝ėę╗Ą─ėŗöĄöĄō■Ż¼×ķ┴╦ĘĮ▒Ń▒╚▌^Ż¼łDųąė├╩«▀MųŲ▒Ē╩ŠĪŻŠÄ┤a║¾Ą─╩«╬╗öĄō■×ķdata10bŻ¼adout╩ŪĮŌ┤a║¾Ą─öĄō■ĪŻ┐╔ęį┐┤ĄĮļmėąčė▀tŻ¼ĮŌ┤a║¾öĄō■╚į×ķėŗöĄöĄō■ĪŻę“┤╦│╠ą“┐╔ęį£╩┤_ĄžīŹ¼FĮŌ┤a╣”─▄ĪŻ

4 ĮY╩°šZ

╚½ļŖęĢą┼╠¢ųą│²┴╦ęĢŅlą┼╠¢═ŌŻ¼▀Ć░³└©ę¶Ņlą┼╠¢Ż¼Ųõ┬Ģ궹┼ŽóĄ─é„▌ö┼c▐DōQ╠Ä└ĒŻ¼╩Ūæ¬ė├ŅIė“ųą▓╗┐╔╚▒╔┘Ą─ā╚╚▌┼c═ĻéõĪŻ│²┴╦å╬Ž“═©ą┼═ŌŻ¼╩š░lįOéõų«ķgŽÓ╗ź▀Mąąą┼ŽóĮ╗ōQŻ¼īŹ¼FļpŽ“═©ą┼Īó═Ļ│╔Ę┤Ž“┐žųŲ╣”─▄Ż¼į┌╣Ō└w═©ą┼æ¬ė├ŅIė“ųą½@Ą├ÅVĘ║æ¬ė├║═Ųš╝░ĪŻ▀@ą®šnŅ}Ą─╝╝ągąį═žš╣┼c▐DōQŻ¼ęŲų▓ĄĮŽÓĻPīŹ“×Į╠īWĄ─æ¬ė├ųąŻ¼ę╗Č©ėąŲõĘeśOĄ─ū„ė├║═ęŌ┴xĪŻ