ÕŠŌŠĢšéTđâŨÓÓĩÆũĘĮÁŋŨÓđâWōÖÐÎđâŨÓĖ―yģĢÓÃĩÄĩþēÉžŊÔOäĢŽÓÃÓÚĘÕžŊÎđâŨÓĖ―yÆũĖ―yĩ―ĩÄÎđâŨÓÐÅĖĄĢÓÉÓÚēŧÍŽĩÄöšÏÐčŌŠÓÃĩ―ēŧÍŽĩÄÓĩÄĢĘ―ĢŽÉĖÓÃĩÄÓĩÆũÍųÍųëyŌÔMŨãūßówĩÄÐčĮóĢŽŧōÕßÔėģÉēÉžŊЧÂĘĩÍÏÂĄĢÏĩ―yēÉÓÃĩÄĘĮŌŧ·NŧųÓÚMicroBlazeÏĩ―yFSLŋūĩÄŋÉUÕđÓĩÆũÔOÓžÜĢŽÔžÜÄÜōė`ŧîĩÄĖížÓēŧÍŽĩÄÓĩđĶÄÜĢŽēĒÍĻß^―yŌŧĩÄFSLŋūšÍMicroblaze CPUÅcPCÍĻÐÅĄĢÔÚÔžÜĩÄŧųĩAÉÏŽFÁËáĶÁŋŨÓÎŨÔÐýÕ{ŋØōÖÐģĢÓÃĩÄÓĩÄĢĘ―ĄĢÏĩ―yËųēÉÓÃĩÄÔOӚ͎F·―Ę―ŋÉŌÔÍÆVĩ―ÆäËûđâŨÓÓĩÐčĮóÖÐĢŽēĒūßÓÐÝ^ĩÍĩÄÔOÓšÍÉúŪaģÉąūĄĢ

0 ŌýŅÔ

đâWîIÓōÓČÆäĘĮÁŋŨÓđâWîIÓōĩÄōģĢģĢÐčŌŠßMÐÐÎÏāļÉđâŨÓĩÄĖ―yÓÃÓÚŽFōĩþĩÄēÉžŊĄĢŌŧ°ãģĢÓÃĩÄÅäÖÃĘĮŌŧÎđâŨÓĖ―yÆũžÓÉÏŌŧéTđâŨÓÓĩÆũĢŽÆäĮ°ķËĩÄÎđâŨÓĖ―yÆũÓÃíĘÕžŊđâŨÓÐÅĖĢŽÃŋĖ―yĩ―ŌŧđâŨÓŪaÉúŌŧTTLÃ}_ĢŽšóķËĩÄéTđâŨÓÓĩÆũÓÃíÓäÔTTLÉÏÉýŅØĩÄŋēĒĮŌÅcPCĩČÆäËûÆũžþÍĻÐÅŧōÕßÍŽē―ĄĢAPDĩÄđĪŨũ·―Ę―ÏāĶšÎĢŽķøéTđâŨÓÓĩÆũtÓÉÓÚūßówōÐčĮóēŧÍŽķøŌŠĮóēŧÍŽĩÄđĪŨũ·―Ę―ĢŽšÜëyÓÐŌŧ·NÍĻÓÃĩÄÓĩÄĢĘ―ÄÜōMŨãļũ·NĮérĩÄÐčĮóĄĢÓÉÓÚģÉąūÏÞÖÆĢŽđĶÄÜđĖķĻĩÄÓĩÆũÍųÍųŌōé]ÓÐVéĩÄĘÐöķøÔėģÉrļņšÜļߥĢÁíŌŧ·―ÃæĢŽđĪIšÍŋÆŅÐ―įŲŲIĩÄÉĖÓÃÓĩÆũÍųÍųo·ĻMŨãŨÔžšĩÄūßówÐčĮóķø§ÖÂđĪŨũЧÂĘĩÍÏÂĢŽÉõÖÁo·ĻMŨãŌŠĮóĄĢ

ËųÖ^éTđâŨÓÓĩÆũūÍĘĮáĶÎŨÔÐýÁŋŨÓÕ{ŋØōŅÐūŋÖÐĶÎđâŨÓĖ―yĩÄÐčĮóËųŅÐÖÆĩÄĄĢÎŨÔÐýÁŋŨÓÕ{ŋØĘĮĶū§ówÖÐĩÄČąÏÝĢŽČįÁŋŨÓücšÍ―ðĘŊÉŦÐÄßMÐÐŋØÖÆĢŽÆäÐÅĖŨxģöŌŧ°ãĘĮÍĻß^ŨÔÐý°lÉúĩÄÎđâŨÓßMÐÐĖ―yŽFĩÄĄĢÔÚīËîōÖÐģĢÓÃĩÄžžÐgÓÐČý·NĢšéTđâŨÓÓĩĄĒķĻrÓĩšÍÏāęPšŊĩyÁŋĄĢÎÄÖÐËųĘöĩÄÏĩ―y―ĻÁĒÁËŌŧ·NŋÉUÕđĩÄÍĻÐÅšÍŋØÖÆžÜÄÜōĖížÓēŧÍŽ·―Ę―ĩÄÓĩđĶÄÜĄĢ

1 Ïĩ―y―YÔOÓ

ÕûówÏĩ―y―YĘūŌâDČįD1ËųĘūĢŽÍĻß^PCCĩÄŌÔĖŦūWŋÚŽFÅcÓĩÏĩ―yĩÄĩþÍĻÓÅcÃüÁîũÝĢŽPCCĒđĪŨũÄĢĘ―ßxņĩČÃüÁîÍĻß^ūWŋÚÏōÏĩ―y°lËÍĢŽķøÏĩ―yĒÔÚēŧÍŽÄĢĘ―ÏÂĩÄÓĩÖĩž°Óĩ îBĩČĩþÍĻß^ūWŋÚ°lËÍĩ―PCCĢŽ―ŧÓÉPCCĶĩþßMÐÐĖĀíĄĢÏĩ―yĩÄÖũÐūÆŽēÉÓÃXilinxĩÄSPARTAN 3EÏĩÁÐĩÄXC3S500EĄĢÏĩ―yĩÄđâŨÓÓĩÝČëÓÉÉBNC―ÓŋÚŌýČëĢŽß@É―ÓŋÚŋÉŌÔÓÉFPGAßMÐÐÅäÖÃĢŽĘđđâŨÓÓĩÆũŌÔēŧÍŽĩÄÄĢĘ―ßMÐÐđĪŨũĄĢÏĩ―yĩÄđĖžþýÔÚFLASHÐūÆŽČĢŽSDRAMĖáđĐÁËīóČÝÁŋīæĶŋÕégĢŽÓÃÓÚß\ÐÐrŅbÝdMicroblazeÜšËīúīaĄĒÓĩŠÓÃīúīaŌÔž°īæĶÓĩĩÄĩþĄĢ

Ïĩ―yŌÔFPGAéĖĀíÖÐÐÄĢŽŽFļũ·NđĪŨũÄĢĘ―ĢŽÆäđĶÄÜŋōDČįD2ËųĘūĄĢđĶÄÜÄĢKÖũŌŠ°üĀĻÜšËMicroblazeĄĒĶÍâēŋīæĶÆũĩÄ―ÓŋÚMPMCĄĒŌÔž°ÐčŌŠÔOÓŽFĩÄCounterpulse IPšËĄĢÔÚCounterpulse IPšËÅcĖĀíÆũÜšËÖŪégĢŽēÉÓÃÁËFSLŋūßMÐÐßB―ÓĢŽŽFÓÉMicrobalzeĶCounterpu-lsešËĩÄÅäÖÃĢŽŌÔž°ÓÉCounterpulsešËĩ―MicroblazeĩÄĩþũÝĄĢ

Ïĩ―yđĪŨũrĢŽÓÉMicroblazeÜšËÍĻß^ūWŋÚ―ÓĘÕÓÉPCC°lËÍíĩÄÃüÁîĢŽļųþÃüÁîĢŽÍĻß^Ōŧ·FSLŋūĶđâŨÓÓĩIPšËßMÐÐđĪŨũÄĢĘ―ĩÄßxņšÍÅäÖÃĄĢÓĩIPšËĶÍâēŋÓĩÔīßMÐÐÓĩĢŽÓĩĩÄ―YđûšÍ îBĩþÍĻß^ÁíŌŧ·FSLŋū°lËÍĩ―MicroblazeÜšËĢŽÓÉMicroblazeÜšËĒÔĩþÔÚDDRRAMČßMÐÐū_ĢŽēĒÍĻß^ūWŋÚĒß@ÐĐĩþŨî―K°lËÍ―oPCCĢŽÓÉPCCßMÐзÖÎöĖĀíĄĢ

Ïĩ―yÓÐČý·NđĪŨũÄĢĘ―ĢšÄĢĘ―ŌŧĢšĘđÄÜÓĩĢŽĘđÄÜÐÅĖÓÐЧr(ļßëÆ―ÓÐЧ)ĢŽĶđâŨÓÓĩÝČëĩÄÓĩÃ}_ÐÅĖßMÐÐÓĩĢŧÄĢĘ―ķþĢšķĻÖÜÆÚÓĩĢŽļųþÔOķĻĩÄÓĩÖÜÆÚĢŽĶđâŨÓÓĩÝČëĩÄÓĩÃ}_ÐÅĖßMÐÐÓĩĢŧÄĢĘ―ČýĢšĒÓšÍÍĢÖđÐÅĖ·Öé_ĩÄÓrĢŽļųþÝČëĩÄÓĩĒÓÐÅĖšÍÓĩÍĢÖđÐÅĖ(ūųéÉÏÉýŅØÓÐЧ)ĢŽßMÐÐŌÔÏĩ―yŧųîléŧųĘĩÄÓrĢŽŌÔŽFšŊĩyÁŋĄĢ

2 Ïĩ―yÔOÓŽF

2.1 Ïĩ―yÓēžþŋōD

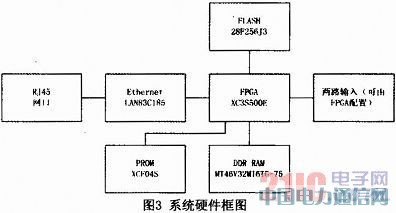

ÓĩÏĩ―yÓēžþ―YČįD3ËųĘūĢŽÓÉFPGAĄĒ64MBĩÄDDRīæĶÆũĄĒ16MBĩÄFLASHīæĶÆũšÍ10M/100MŌÔĖŦÎïĀíÓ(PHY)ĩČ―MģÉĄĢÏĩ―yđĪŨũrĢŽÓÉPCCÍĻß^ūWŋÚ°lËÍÃüÁîĩ―FPGAĢŽFPGAČēŋĩÄMicroblazeÜšËÅäÖÃÓĩIPšËĩÄđĪŨũÄĢĘ―ĢŽÓÉFPGAÍĻß^É·BNC―ÓŋÚĶÍâēŋÓĩÔīßMÐÐÓĩĢŽēĒĒĩþÔÚDDRRAMČßMÐÐū_ĢŽŨî―KĒß@ÐĐĩþÍĻß^ūWŋÚ°lËÍĩ―PCCĄĢ

2.2 ÖũŌŠÔŠÆũžþ―é―B

2.2.1 FPGAÐūÆŽž°ÆäÅäÖÃÐūÆŽßxÓÃ

FPGAßxÓÃXilinxđŦËūĩÄSpartan-3EÏĩÁÐXC3S500EĢŽēÉÓÃÏČßMĩÄ90nmÖÆÔėđĪËÉúŪaĢŽÆäÆũžþÃÜķČé50ČféTĄĢSpartan3ÏĩÁÐĩÄFPGAĘĮXilinxđŦËūĢéTáĶīóČÝÁŋĄĒĩÍģÉąūÐčĮóĩÄëŨÓÔOÓķøé_°lĩÄĢŽŋÉÖ§ģÖķā·NëÆ―ĩÄI/OËĘĢŧšŽÓÐØSļŧĩÄßÝŲYÔīĄĢXC3S500EūßÓÐ360kbitsĩÄKRAMĄĒ73kbitsĩÄ·ÖēžĘ―RAMĄĒ10476ßÝÎÔŠĄĒ2018×18ĩÄģË·ĻÆũšÍ4DCMrįđÜĀíÄĢKĄĢ

FPGAĩÄÅäÖÃÐūÆŽßxÓÃĩÄĘĮXilinxđŦËūĩÄÔÚÏĩ―yŋÉūģĖÅäÖÃÐūÆŽXCF04SĢŽÔÐūÆŽŋÉéXC3S500EĖáđĐŌŨÓÚĘđÓÃĄĒģÉąūĩÍĮŌŋÉÖØÍūģĖĩÄÅäÖÃĩþīæŲA·―·ĻĢŽÔÐūÆŽÖ§ģÖIEEE1149.1ËĘĩÄJTAGß

―įßÃčyÔšÍūģĖĄĢÔÚąūÏĩ―yÔOÓÖÐĢŽXCF04SÖũŌŠīæ·ÅÓÃÓÚŌý§Microblazeܚ˞°ŠÓÃģĖÐōĩÄŌý§īúīaĄĢ

2.2.2 īæĶÐūÆŽ

Ïĩ―yĘđÓÃĩÄRAMĘĮMicron TechnologyđŦËūĩÄDDRSDRAM(MT46V32M16)ĢŽĘĮŌŧÆŽČÝÁŋé512Mbit(32Mx16)ĩÄ16ÎŧŋūķČīæĶÐūÆŽĢŽÓÃÓÚÉÏëšóžÓÝdMicroblazeÜšËīúīašÍŠÓÃģĖÐōīúīaĢŽŌÔž°ĶÓĩĩþßMÐÐū_ĄĢFLASHÐūÆŽĘĮIntel StrataFlash parallel NORFlashĢŽÐÍĖé28F256J3ĢŽīæĶÃÜķČé256MbitĢŽÔÚąūÏĩ―yÖÐÓÃÓÚąĢīæMicroblazeÜšËīúīašÍŠÓÃģĖÐōīúīaĄĢ

3 đĶÄÜÔOÓŽF

3.1 ŧųÓÚEDKĩÄFPGAÜšËMicroblazeĩÄŠÓÃÔOÓŽF

Ïĩ―yÔOÓđĪūßÖũŌŠēÉÓÃXilinxđŦËūĩÄĮķČëĘ―é_°lĖŨžþEDKĢŽËüĘĮÓÃÓÚÔOÓĮķČëĘ―ĖĀíÏĩ―yĩÄžŊģÉ―âQ·―°ļĄĢËü°üĀĻīî―ĻÓēžþÆ―Å_ĩÄXPSšÍßMÐÐÜžþÅäÖÃĩÄSDKĄĢ

MicroblazeĘĮXilinxđŦËūÍÆģöĩÄ32ÎŧÜĖĀíÆũšËĢŽÖ§ģÖCoreConnectŋūĩÄËĘÍâÔOžŊšÏĄĢMicroBlazeĖĀíÆũß\ÐÐÔÚ150MHzrįÏÂĢŽŋÉĖáđĐ125 D-MIPSĩÄÐÔÄÜĢŽß@·NļßЧĩÄÜšËÔÚąūÏĩ―yÖÐŋÉÓÃÓÚŽFĖĀíÆũđĶÄÜĢŽŽFĶÓĩIPšËĩÄÅäÖÃĢŽŌÔž°Ö§ÎXilinxĩÄclockgeneratorĄĒEt-hernetĩČIPšËĄĢÏĩ―yĶÓĩÆũĩÄŽFēÉÓÃVerilogÕZŅÔĒÓĩđĶÄÜūéIPšËĢŽĒÆäÍĻß^FSLŋūėÔÚMicroblazeÜšËÉÏĢŽŌÔŽFÓĩđĶÄÜĄĢ

3.2 ÍĻÓ

fŨh

Microblazeĩ―ÓĩIPšËÖŪégĩÄÍĻÓĩþķĻÁxČįÏÂĢš

ÓĩIPšËĩ―MicroblazeÖŪégĩÄÍĻÓĩþķĻÁxČįÏÂĢš

3.3 ÓĩIPšËĩÄÔOÓŽF

3.3.1 ÓĩIPšËĩÄ―Y

ÓĩIPšËēÉÓÃverilogÓēžþÕZŅÔūĢŽÆä―YČįD6ËųĘūĢŽíÓÎÄžþcounterpulse3Ķ―ÓŋÚßMÐÐÅäÖÃĢŽēĒļųþFSLŋūÉÏĩÄÃüÁî

ĒĩßxņđĪŨũÄĢĘ―ĢŽpulsecount1ĄĒpulsecount2šÍpulsecount3·ÖeĘĮ3·NđĪŨũÄĢĘ―ĩÄīúīaŽFĢŽfsloprtĘĮÅcFSLßMÐÐ―ÓŋÚĩÄīúīaĄĢ

3.3.2 ÅcFSLŋū―ÓŋÚ

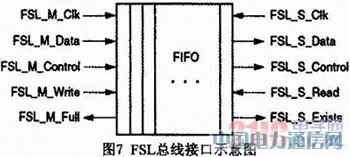

fslopn.vĩÄīúīaÍęģÉÅcFSLŋū―ÓŋÚđĶÄÜĄĢFSLŋūĘĮÎÏōücĶücĩÄÍĻĩĀĢŽËüÓÃÓÚÍęģÉČÎŌâFPGAÖÐÉÄĢKĩÄŋėËŲÍĻÓĄĢFSLŋūĘĮŧųÓÚFIFOĩÄĢŽŧųÓÚ·ĮđēÏíĩÄoÖŲēÃÍĻÐÅCÖÆĢŽËüĩÄÉîķČĘĮŋÉŌÔÔOÖÃĩÄĢŽŨîīóŋÉŌÔĩ―8kĢŽūßäļßËŲĩÄÍĻÐÅÐÔÄÜĢŽÆä―YČįD7ËųĘūĄĢ

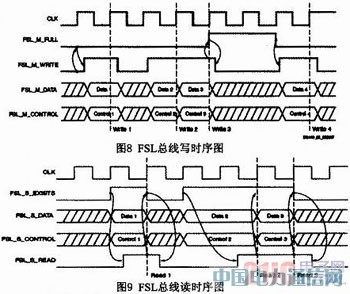

ÓÉÓÚFSLŋūĘĮÎÏōĩÄĢŽËųŌÔÏĩ―yÖÐēÉÓÃÁËÉlFSLŋūĢŽŽFMieroblazeĩ―ÓĩIPšËÖŪégĩÄëpÏōÍĻÓĢŽÓĩIPšËÔÚÃæĶÉlFSLŋūrĢŽúŪĩÄ·ÖeĘĮMASTER(Öũ)šÍSLAVE(Ä)É·N―ĮÉŦĄĢŌōīËĢŽfsloprt.vĩÄīúīaŠÔÍŽrMŨãÅcFSLŋū―ÓŋÚĩÄŨxšÍrÐōĄĢŨxrÐōČįD8šÍD9ËųĘūĄĢ

3.4 ÓĩIPšËšÍFSLŋūĩÄÔÚEDKÖÐĩÄßB―ÓŽF

éÁËÄÜĘđÓÃFSLŋūĢŽĘŨÏČŠÔÔÚXPSDÐÎ―įÃæÖÐĶMicroblazeßMÐÐÅäÖÃĢŽÔÚBusesÖÐĒNumber of FSL LinksÔOÖÃé1ĄĢÔŲÔÚIP CatalogÖÐĒFSLŋūžÓČëĩ―đĪģĖÖÐÉīÎĄĢ

ÔÚÓĩIPšËūšóēĒūCšÏÍĻß^šóĢŽĒÔIPšË§Čëĩ―XPSđĪģĖÖÐĄĢ

ÔÚXPSÖÐĢŽ·ÖeĶMicroblazešÍÓĩIPšËĩÄMFSLšÍSFSLßMÐÐßB―ÓĢŽĒMicroblazeĩÄMFSLķËßB―Óĩ―ÓĩIPšËĩÄSFSLķËĢŽ·īÖŪĒÓĩIPšËĩÄMFSLķËßB―Óĩ―MicroblazeĩÄSFSLķËĄĢēĒÔÚsystem.mhsÖÐßMÐÐČįÏÂÅäÖÃĢš

ÓÉÓÚÄÓĩIPĩ―Microblaze·―ÏōĩþÁŋÝ^īóĢŽËųŌÔĶFSLŋūĩÄÉîķČßMÐÐÁËÅäÖÃĢŽČįÉÏĘöīúīaÖÐĢŽPARAMETERC_FSL_DEPTH=128ĢŽąŧÅäÖÃé128žÉîķČĄĢ

4 ―YÕ

ÔÚÏĩ―yĩÄÔOÓÖÐĢŽđâŨÓÓĩIPšËÅcMieroblazeÜšËÖŪégÍĻß^FSLŋūßMÐÐÍĻÓĢŽēĒĮŌĶFSLŋūÉÏĩÄFIFOū_ßMÐÐÁËÉîķČUģäĢŽīóīóÔöÁËđâÓĩĩþĩÄũÝŋÉŋŋÐÔĄĢÓÉÓÚÏĩ―yĒéTđâŨÓÓĩĩÄČý·NÄĢĘ―ĢŽŌÔIPšËĩÄ·―Ę―ŽFĢŽÏāĶÓÚĘÐöÉÏÉĖÓÃĩÄÓĩÆũíÕfĢŽŽF·―Ę―ė`ŧîĢŽŌŨÓÚÅäÖÚÍUÕđĢŽß@·N·―Ę―ééTđâŨÓÆäËûŋÉÄÜÔÚĩÄÓĩÐčĮóÁôÏÂÁËUÕđĩÄŧųĩAĢŽēĒūßÓÐÝ^ĩÍĩÄÔOÓšÍÉúŪaģÉąūĄĢ