š¬ę¬Ż║×ķØMūŃīŹ(sh©¬)ļH╣ż│╠æ¬(y©®ng)ė├Ą─ąĶ꬯¼čąųŲ┴╦ęįŪČ╚ļ╩ĮMC8051ā╚(n©©i)║╦×ķ║╦ą─╝╝ąg(sh©┤)Ą─▒Ńöy╩ĮĘ∙Ņl╠žąį£y(c©©)įćāxĪŻŽĄĮy(t©»ng)ęįXilinx╣½╦Š╔·«a(ch©Żn)Ą─ą═╠¢(h©żo)×ķXC3S400Ą─FPGAąŠŲ¼×ķė▓╝■╠Ä└Ē║╦ą─Ż¼ęįMC8051ā╚(n©©i)║╦ū„×ķė├æ¶Į╗╗źĮń├µįO(sh©©)ėŗ(j©¼)Ą─┐žųŲ║╦ą─ĪŻ▓╔ė├“š²Žę▓ķšę▒ĒIP║╦+D/A”Ą─ĘĮ╩ĮīŹ(sh©¬)¼F(xi©żn)DDS╝╝ąg(sh©┤)▓ó«a(ch©Żn)╔·ŽĄĮy(t©»ng)Æ▀Ņlą┼╠¢(h©żo)Ż¼ęį«É▓ĮFIFOū„×ķFPGA┼cMC8051ā╚(n©©i)║╦ų«ķgöĄ(sh©┤)ō■(j©┤)é„▌ö?sh©┤)─ŠÅ┤µ─ŻēKŻ¼═¼Ģr(sh©¬)▓╔ė├TFT▓╩Ų┴ę║Š¦▀M(j©¼n)ąą’@╩ŠĮń├µįO(sh©©)ėŗ(j©¼)ĪŻ

į┌¼F(xi©żn)┤·ļŖ┴”ļŖūėŽĄĮy(t©»ng)ųąŻ¼ļSų°ā╚(n©©i)ł÷(ch©Żng)£y(c©©)įć║══Ōł÷(ch©Żng)ŠSūo(h©┤)╣żū„┴┐Ą─į÷╝ėŻ¼ī”(du©¼)─┐Ū░═©ė├Ą─£y(c©©)įćāxŲ„ę▓╠ß│÷┴╦ą┬Ą─ę¬Ū¾Ż¼čąųŲĄ═│╔▒ŠĪó¾wĘeąĪĄ─▒Ńöy╩ĮĘ∙Ņl╠žąį£y(c©©)įćāxŠ▀ėą╔Ņ▀h(yu©Żn)Ą─¼F(xi©żn)īŹ(sh©¬)ęŌ┴xĪŻ─┐Ū░Ż¼ĮY(ji©”)║Žą┬ą═╬ó╠Ä└ĒŲ„ąŠŲ¼▀M(j©¼n)ąąĘ∙Ņl╠žąį£y(c©©)įćāxĄ─čąųŲų„ę¬ėą╚²ĘN╝╝ąg(sh©┤)═ŠÅĮŻ║(1)▓╔ė├å╬Ų¼ÖC(j©®)ū„×ķų„┐žąŠŲ¼Ż¼═©▀^▄ø╝■ŠÄ│╠ĘĮ╩ĮīŹ(sh©¬)¼F(xi©żn)▓┐Ęųė▓╝■╣”─▄Ż¼▀@ĘNĘĮ░Ė┐╔ęįėąą¦ĮĄĄ═ŽĄĮy(t©»ng)Ą─Å═(f©┤)ļsČ╚Ż¼Ą½į┌īŹ(sh©¬)Ģr(sh©¬)ąį╔Ž▓╗▒M╚╦ęŌĪŻ(2)æ¬(y©®ng)ė├┐╔ŠÄ│╠▀ē▌ŗŲ„╝■(╚ńFPGA)▀M(j©¼n)ąąįO(sh©©)ėŗ(j©¼)┐╔ęįėąą¦ĮŌøQĖ▀╦┘öĄ(sh©┤)ō■(j©┤)┴„Ą─īŹ(sh©¬)Ģr(sh©¬)╠Ä└Ēå¢Ņ}Ż¼Ą½į┌╚╦ÖC(j©®)Įń├µĄ─įO(sh©©)ėŗ(j©¼)ųąŠ▀ėą▌^┤¾└¦ļyĪŻ(3)▓╔ė├å╬Ų¼ÖC(j©®)┼cFPGAąŠŲ¼ĮY(ji©”)║ŽĄ─ĘĮ╩ĮŻ¼═©▀^═Ō▓┐┐éŠĆ▀BĮė║═öĄ(sh©┤)ō■(j©┤)é„▌öģf(xi©”)ūhĄ─įO(sh©©)ėŗ(j©¼)Ż¼╩╣Ą├ŽĄĮy(t©»ng)╝µŠ▀ā╔š▀Ą─ā×(y©Łu)ä▌(sh©¼)Ż¼Å─Č°│╔×ķįO(sh©©)ėŗ(j©¼)╚╦åT╩ū▀xĄ─ų„┴„ĘĮ░ĖĪŻ

¼F(xi©żn)┤·EDA(Electronic Design Automation)╝╝ąg(sh©┤)Ą─░l(f©Ī)š╣║═┤¾ęÄ(gu©®)─ŻFPGAŲ„╝■Ą─═Ų│÷Ż¼╩╣Ą├į┌å╬Ų¼F(xi©żn)PGAąŠŲ¼ųą▀M(j©¼n)ąąŪČ╚ļ╩Į8051 IP║╦įO(sh©©)ėŗ(j©¼)│╔×ķ┐╔─▄ĪŻæ¬(y©®ng)ė├¼F(xi©żn)┤·EDA╝╝ąg(sh©┤)Ż¼ęįFPGAŲ„╝■×ķė▓╝■ŲĮ┼_(t©ói)Ż¼╩╣ė├VHDLšZčįŠÄ│╠Ż¼┐╔ęįīŹ(sh©¬)¼F(xi©żn)┼cMCS-51ŽĄ┴ąå╬Ų¼ÖC(j©®)ųĖ┴ŅŽĄĮy(t©»ng)═Ļ╚½╝µ╚▌Ą─╬ó┐žųŲŲ„ąŠŲ¼IP(Intellectual Property)║╦[1]ĪŻ▒Š╬─ęį┤╦×ķ╗∙ĄA(ch©│)Ż¼╠ß│÷┴╦Ę∙Ņl╠žąį£y(c©©)įćāxįO(sh©©)ėŗ(j©¼)Ą─ą┬═ŠÅĮĪŻŽĄĮy(t©»ng)ęįFPGA×ķ║╦ą─▓╔╝»╠Ä└Ē─ŻēKŻ¼ęįO(sh©©)regano╣½╦Šķ_░l(f©Ī)Ą─ŪČ╚ļ╩ĮMC8051ā╚(n©©i)║╦Ż©ęįŽ┬║åĘQ51ā╚(n©©i)║╦Ż®×ķ’@╩Š┐žųŲ║╦ą─Ż¼═©▀^FPGAā╚(n©©i)▓┐Ą─š²Žę▓ķšę▒ĒIP║╦═Ō╝ėD/A─ŻēKĄ─╦╝Žļ«a(ch©Żn)╔·ŽĄĮy(t©»ng)ąĶꬥ─Æ▀Ņlą┼╠¢(h©żo)į┤Ż¼═¼Ģr(sh©¬)▓╔ė├2.4ėó┤ńTFT▓╩Ų┴ę║Š¦’@╩ŠŲ„▀M(j©¼n)ąą╚╦ÖC(j©®)Įń├µįO(sh©©)ėŗ(j©¼)Ż¼īŹ(sh©¬)¼F(xi©żn)┴╦▒Ńöy╩ĮĘ∙Ņl╠žąį£y(c©©)įćāxĄ─╗∙▒Š╣”─▄ĪŻįōāxŲ„Š▀ėąąĪą═╗»ĪóŅlĦīÆĪó▓┘ū„║åå╬Īó£y(c©©)┴┐Š½┤_Č╚Ė▀ĪóĮń├µ’@╩Šėč║├Ą╚ā×(y©Łu)³c(di©Żn)Ż¼Š▀ėąÅVķ¤Ą─æ¬(y©®ng)ė├┐šķgĪŻ

1 ŽĄĮy(t©»ng)ĮM│╔┼c╣żū„įŁ└Ē

1.1 ŽĄĮy(t©»ng)ĮM│╔

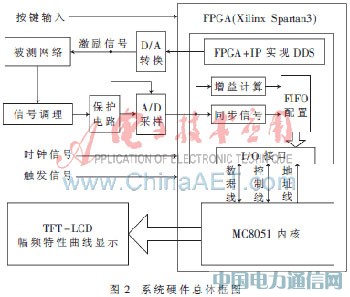

ŽĄĮy(t©»ng)ų„ę¬ė╔š²Žę╝żäŅ(l©¼)ą┼╠¢(h©żo)Ą─«a(ch©Żn)╔·─ŻēK║═ą┼╠¢(h©żo)▓╔╝»Īó╠Ä└Ē║═īŹ(sh©¬)Ģr(sh©¬)’@╩Š─ŻēKĮM│╔ĪŻŲõųąŪ░š▀▓╔ė├╗∙ė┌“IP║╦+Ė▀╦┘D/A”Ą─╦╝Žļ«a(ch©Żn)╔·Æ▀Ņlą┼╠¢(h©żo)Ż¼║¾š▀ų„ę¬░³└©FPGA║╦ą─░ÕĪóļp┬ĘĖ▀╦┘A/Dęį╝░╚╦ÖC(j©®)Į╗╗źĮń├µĪŻį┌ŽĄĮy(t©»ng)Ģr(sh©¬)ńŖ║═ė|░l(f©Ī)ą┼╠¢(h©żo)Ą─“ī(q©▒)äė(d©░ng)Ž┬Ż¼═¼Ģr(sh©¬)▓╔╝»┤²£y(c©©)ŠW(w©Żng)Įj(lu©░)Ą─▌ö│÷ą┼╠¢(h©żo)ęį╝░ŽĄĮy(t©»ng)Ą─╝żäŅ(l©¼)ą┼╠¢(h©żo)Ż¼▓ó▀M(j©¼n)ąąŽÓæ¬(y©®ng)Ą─öĄ(sh©┤)ō■(j©┤)╠Ä└ĒŻ¼īŹ(sh©¬)¼F(xi©żn)ī”(du©¼)ėąį┤╗“¤oį┤╦─Č╦ŠW(w©Żng)Įj(lu©░)Ą─Ę∙Ņl╠žąį£y(c©©)įćĪŻŽĄĮy(t©»ng)ĮM│╔┐“łD╚ńłD1╦∙╩ŠĪŻ

ŽĄĮy(t©»ng)įO(sh©©)ėŗ(j©¼)ųąąĶę¬ĮŌøQĄ─║╦ą─å¢Ņ}Ż║(1)51ā╚(n©©i)║╦Ą─│§╩╝╗»┼õų├å¢Ņ}ĪŻŽĄĮy(t©»ng)╩╣ė├Ą─51ā╚(n©©i)║╦Ż¼┐╔ęįų▒Įė═©▀^Ēöīė╬─╝■Ą─Č╦┐┌└²╗»īŹ(sh©¬)¼F(xi©żn)┼cFPGAā╚(n©©i)▓┐Č©┴xą┼╠¢(h©żo)ų«ķgĄ─▀BĮėŻ¼Č°51ā╚(n©©i)║╦╩╣ė├Ą─┤µā”(ch©│)Ų„─ŻēKätąĶę¬ė├æ¶▀M(j©¼n)ąą┼õų├ĪŻ(2)öĄ(sh©┤)ō■(j©┤)┴„Ą─╦┘┬╩Ųź┼õå¢Ņ}ĪŻĮø(j©®ng)A/D▓╔╝»Ą├ĄĮĄ─öĄ(sh©┤)ō■(j©┤)┬╩▀h(yu©Żn)▀h(yu©Żn)│¼│÷┴╦51ā╚(n©©i)║╦Ą─▀\(y©┤n)╦Ń╠Ä└Ē─▄┴”Ż¼ę“┤╦ŽĄĮy(t©»ng)ųąę¬▀M(j©¼n)ąąöĄ(sh©┤)ō■(j©┤)ŠÅ┤µ─ŻēKĄ─įO(sh©©)ėŗ(j©¼)ĪŻ(3)▓╩Ų┴ę║Š¦Ą─’@╩Š┐žųŲĪŻ’@╩Š▓┐Ęų╩ŪįōāxŲ„Ą─ĻP(gu©Īn)µI─ŻēKŻ¼ŽĄĮy(t©»ng)▓╔ė├TFT-LCD’@╩Š╝╝ąg(sh©┤)Ż¼┐╔ęį▀M(j©¼n)ąąėč║├Ą─╚╦ÖC(j©®)Įń├µįO(sh©©)ėŗ(j©¼)Ż¼Ą½╩Ū▓╩Ų┴ę║Š¦Ą─│§╩╝╗»Ģr(sh©¬)ą“śOŲõÅ═(f©┤)ļsŻ¼į┌äė(d©░ng)æB(t©żi)Ū·ŠĆ║═£y(c©©)┴┐öĄ(sh©┤)ō■(j©┤)Ą─īŹ(sh©¬)Ģr(sh©¬)’@╩ŠĘĮ├µę¬▀M(j©¼n)ąąā×(y©Łu)╗»įO(sh©©)ėŗ(j©¼)ĪŻ▀@ą®å¢Ņ}į┌īŹ(sh©¬)ļHįO(sh©©)ėŗ(j©¼)ųąŠ∙Ą├ĄĮ┴╦║Ž└ĒĮŌøQĪŻ

1.2 £y(c©©)┴┐įŁ└Ē

ī”(du©¼)ė┌ę╗éĆ(g©©)ŠĆąįĢr(sh©¬)▓╗ūā(LTI)ŽĄĮy(t©»ng)Ż¼Ųõø_╝żĒææ¬(y©®ng)×ķh(t)Ż¼į┌╝żäŅ(l©¼)×ķš²Žęą┼╠¢(h©żo)e(t)=Acos(?ūž0t+?ŲØ)Ģr(sh©¬)Ż¼ŽĄĮy(t©»ng)Ą─┴ŃĀŅæB(t©żi)Ēææ¬(y©®ng)×ķŻ║

ė╔┤╦┐╔ęį┐┤│÷Ż¼ŽĄĮy(t©»ng)▌ö│÷Ą─ĘĆ(w©¦n)æB(t©żi)Ēææ¬(y©®ng)ę▓╩Ūę╗éĆ(g©©)š²Žęą┼╠¢(h©żo)Ż¼ŲõŅl┬╩║═▌ö╚ļą┼╠¢(h©żo)Ą─Ņl┬╩ŽÓ═¼Ż¼Ą½Ę∙Č╚║═ŽÓ╬╗░l(f©Ī)╔·┴╦ūā╗»Ż¼ŲõųąĘ∙Č╚ūā?y©Łu)ķįŁ╝żä?l©¼)ą┼╠¢(h©żo)Ę∙Č╚Ą─|H(j?ūž0)|▒ČŻ¼|H(j?ūž0)|ĘQ×ķļŖ┬ĘŠW(w©Żng)Įj(lu©░)Ę∙Ņl╠žąįĪŻ

ŽĄĮy(t©»ng)╣żū„Ģr(sh©¬)Ż¼īóĄ╚Ę∙Ą─š²ŽęÆ▀Ņlą┼╠¢(h©żo)ū„×ķ▌ö╚ļą┼╠¢(h©żo)╝żäŅ(l©¼)▒╗£y(c©©)ŠW(w©Żng)Įj(lu©░)ĪŻÆ▀Ņlą┼╠¢(h©żo)Ą─Ų╩╝Ņl┬╩ĪóĮKų╣Ņl┬╩ĪóŅl┬╩▓Į▀M(j©¼n)ųĄęį╝░Æ▀├ĶĢr(sh©¬)ķgŠ∙┐╔ęį═©▀^░┤µI▌ö╚ļĄ─ĘĮ╩ĮįO(sh©©)ų├Ż¼ę▓┐╔ęį▓╔ė├ŽĄĮy(t©»ng)─¼šJ(r©©n)Ą─įO(sh©©)ų├ĘĮ╩Į(Æ▀ŅlĘČć·1kHz~1MHzŻ¼Ņl┬╩▓Į▀M(j©¼n)1kHzŻ¼Æ▀├ĶĢr(sh©¬)ķg1s)ĪŻĖ▀╦┘A/D▓╔╝»ŠW(w©Żng)Įj(lu©░)Ą─▌ö│÷ą┼╠¢(h©żo)║═įŁ╩╝╝żäŅ(l©¼)ą┼╠¢(h©żo)Ż¼▓óį┌FPGAā╚(n©©i)═©▀^ĘÕųĄÖz▓©│╠ą“Ą├ĄĮŠW(w©Żng)Įj(lu©░)▌ö│÷ą┼╠¢(h©żo)Ą─░³Įj(lu©░)öĄ(sh©┤)ō■(j©┤)Ż¼═¼Ģr(sh©¬)┼c╝żäŅ(l©¼)ą┼╠¢(h©żo)Ą─Ę∙ųĄ▒╚▌^ėŗ(j©¼)╦Ń▓╗═¼Ņl³c(di©Żn)Ą─į÷ęµöĄ(sh©┤)ō■(j©┤)ĪŻ▓╔ė├«É▓ĮFIFOū„×ķFPGA┼c51ā╚(n©©i)║╦ų«ķgé„▌ööĄ(sh©┤)ō■(j©┤)Ą─ŠÅø_Ų„Ż¼▓óīóŲõ┼õų├×ķ“Ų╣┼ę”╣żū„─Ż╩ĮĪŻ«ö(d©Īng)ė|░l(f©Ī)ą┼╠¢(h©żo)ĄĮüĒĢr(sh©¬)Ż¼īóį÷ęµöĄ(sh©┤)ō■(j©┤)░┤ššę╗Č©Ą─Ė±╩Į║═╦┘┬╩īæ╚ļ«É▓ĮFIFOĪŻ«ö(d©Īng)FIFOųą┤µā”(ch©│)ę╗Č©öĄ(sh©┤)┴┐Ą─öĄ(sh©┤)ō■(j©┤)ęį║¾Ż¼į┌51ā╚(n©©i)║╦═¼▓ĮĢr(sh©¬)ńŖĄ─┐žųŲŽ┬īóöĄ(sh©┤)ō■(j©┤)ūx│÷▓ó╦══∙LCD─ŻēKŻ¼═¼Ģr(sh©¬)Į¹ų╣öĄ(sh©┤)ō■(j©┤)└^└m(x©┤)īæ╚ļFIFOŻ¼īŹ(sh©¬)¼F(xi©żn)Ę∙Ņl╠žąįŪ·ŠĆĄ─’@╩ŠĪŻ

2 ŽĄĮy(t©»ng)ė▓╝■įO(sh©©)ėŗ(j©¼)

ŽĄĮy(t©»ng)ė▓╝■ų„ę¬īŹ(sh©¬)¼F(xi©żn)š²ŽęÆ▀Ņlą┼╠¢(h©żo)Ą─«a(ch©Żn)╔·ĪóŠW(w©Żng)Įj(lu©░)▌ö│÷ą┼╠¢(h©żo)Ą─▓╔╝»╠Ä└ĒĪóöĄ(sh©┤)ō■(j©┤)Ą─é„▌öęį╝░TFTę║Š¦─ŻēKĮė┐┌ļŖ┬ĘĄ╚╣”─▄Ż¼ė▓╝■┐é¾w┐“łD╚ńłD2╦∙╩ŠĪŻ

2.1 FPGA║╦ą─░Õ─ŻēK

FPGA║╦ą─░Õ─ŻēK╩ŪŽĄĮy(t©»ng)Ą─║╦ą─Ż¼Ė∙ō■(j©┤)ąĶę¬įO(sh©©)ėŗ(j©¼)│÷FPGAūŅąĪŽĄĮy(t©»ng)░Õęį╝░ŽÓĻP(gu©Īn)Ą─A/DĪóD/AļŖ┬ĘĪŻŲõųąŻ¼F(xi©żn)PGAūŅąĪŽĄĮy(t©»ng)░Õ▓╔ė├Xilinx╣½╦ŠSpartan3ŽĄ┴ąĄ─XC3S400-PQ208ą═40╚fķTąŠŲ¼Ż¼║╦ą─░Õ▓╔ė├5V▌ö╚ļŻ¼ė╔3Ų¼AMS1117īŹ(sh©¬)¼F(xi©żn)5VĄĮ3.3VĪó5VĄĮ2.5V║═5VĄĮ1.2VĄ─ļŖŲĮ▐D(zhu©Żn)ōQĪŻ░Õ╔Ž▓╔ė├40MHzėąį┤Š¦š±Ż¼ØMūŃĖ▀╦┘įO(sh©©)ėŗ(j©¼)ę¬Ū¾ĪŻA/D×ķADI╣½╦ŠĖ▀╦┘─Ż/öĄ(sh©┤)▐D(zhu©Żn)ōQąŠŲ¼AD9224Ż¼Š▀ėą12╬╗Š½Č╚Ż¼Ūę╣”║─Ą═ĪŻD/A▓╔ė├Ė▀ąį─▄Ė▀╦┘┬╩Ą─AD9764ARąŠŲ¼Ż¼įōąŠŲ¼Š▀ėą14╬╗Ęų▒µ┬╩║═śO╝čĄ─äė(d©░ng)æB(t©żi)¤oļs▓©╩¦šµĘČć·ĪŻ

2.2 Æ▀Ņlą┼╠¢(h©żo)į┤įO(sh©©)ėŗ(j©¼)

Æ▀Ņlą┼╠¢(h©żo)į┤Ą─ąį─▄ųĖś╦(bi©Īo)ų▒Įėė░ĒæāxŲ„Ą─£y(c©©)įćŠ½Č╚Ż¼▒Š╬─▓╔ė├DDS╝╝ąg(sh©┤)«a(ch©Żn)╔·Æ▀Ņlą┼╠¢(h©żo)ĪŻ▀@└’ėąā╔Śl═ŠÅĮ┐╔╣®▀xō±Ż¼ę╗ĘN╩Ū▓╔ė├īŻė├Ą─DDSąŠŲ¼Ż¼╚ńAD9854Ą╚Ż¼└¹ė├FPGA░l(f©Ī)╦═Ņl┬╩┐žųŲūų«a(ch©Żn)╔·Æ▀Ņlą┼╠¢(h©żo)Ż╗┴Ēę╗ĘN╩Ū▓╔ė├FPGAųą╝»│╔Ą─š²Žę▓ķįā▒ĒIP║╦Ż¼▀@╩Ūę╗ĘN└¹ė├“IP║╦+D/A”ŽÓĮY(ji©”)║ŽüĒīŹ(sh©¬)¼F(xi©żn)DDS╝╝ąg(sh©┤)Ą─ĘĮĘ©Ż¼į┌│õĘų╠ßĖ▀FPGAā╚(n©©i)▓┐┘Yį┤└¹ė├┬╩Ą─Ū░╠ߎ┬Ż¼ėų┐╔ęįėąą¦ĮĄĄ═ŽĄĮy(t©»ng)Ą─ė▓╝■Å═(f©┤)ļsČ╚║═│╔▒ŠŻ¼ę“┤╦ŽĄĮy(t©»ng)▓╔ė├įōĘĮ╩Į

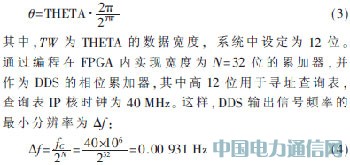

įO(sh©©)ėŗ(j©¼)Łh(hu©ón)Š│╩╣ė├Xilinx╣½╦ŠĄ─ISE7.1Ż¼═©▀^Core Generator╔·│╔š²Žę▓ķįā▒ĒIP CoreŻ¼▓ķįā▒ĒųąĄ─▓©ą╬öĄ(sh©┤)ō■(j©┤)┤µā”(ch©│)į┌FPGAĄ─ēK┤µā”(ch©│)Ų„(Block Memory)ųąĪŻ▓ķįā▒ĒIP║╦Ą─▌ö╚ļŽÓ╬╗┐žųŲūųTHETA┼cīŹ(sh©¬)ļHŽÓ╬╗ų«ķgĄ─ĻP(gu©Īn)ŽĄ×ķŻ║

įōŅl┬╩Š½Č╚═Ļ╚½▀_(d©ó)ĄĮįO(sh©©)ėŗ(j©¼)ę¬Ū¾ĪŻ

2.3 ŽĄĮy(t©»ng)Įė┐┌─ŻēK

į┌įōŽĄĮy(t©»ng)ųąŻ¼ę║Š¦─ŻēK▓╔ė├ILI9320Ų¼╔ŽŽĄĮy(t©»ng)(SoC)“ī(q©▒)äė(d©░ng)Ų„[2]Ż¼Ņü╔½’@╩Š╔ŅČ╚×ķ18╬╗Ż¼Ęų▒µ┬╩×ķ240RGB×320Ž±╦žĪŻŽĄĮy(t©»ng)▓╔ė├i80┐éŠĆĮY(ji©”)śŗ(g©░u)┐žųŲę║Š¦’@╩ŠŻ¼╝┤═©▀^ūx╩╣─▄(RDB)║═īæ╩╣─▄(WRB)ā╔Śl┐žųŲŠĆ▀M(j©¼n)ąąūxīæ▓┘ū„Ż¼öĄ(sh©┤)ō■(j©┤)ŠĆĄ─īÆČ╚×ķ8╬╗ĪŻę║Š¦─ŻēKųąĄ─┐žųŲą┼╠¢(h©żo)║═öĄ(sh©┤)ō■(j©┤)ą┼╠¢(h©żo)Š∙×ķś╦(bi©Īo)£╩(zh©│n)Ą─TTLļŖŲĮŻ¼┐╔ęįų▒Įė┼cFPGAĄ─I/OĮė┐┌ŽÓ▀BĪŻ

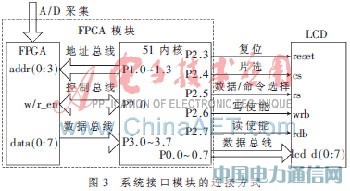

51ā╚(n©©i)║╦Š▀ėą8╬╗┐éŠĆīÆČ╚Ż¼═©▀^ā╚(n©©i)▓┐Č╦┐┌ė│╔õĄ─ĘĮ╩ĮīŹ(sh©¬)¼F(xi©żn)┼cFPGA─ŻēKĄ─Įė┐┌▀BĮėĪŻ×ķ┴╦īŹ(sh©¬)¼F(xi©żn)FPGA▓╔╝»öĄ(sh©┤)ō■(j©┤)Ą─īŹ(sh©¬)Ģr(sh©¬)é„▌ö║═’@╩ŠŻ¼į┌Įė┐┌įO(sh©©)ėŗ(j©¼)ųą│²┴╦öĄ(sh©┤)ō■(j©┤)┐éŠĆ(data)ęį═ŌŻ¼▀ĆąĶꬥžųĘ┐éŠĆ(addr)║═┐žųŲ┐éŠĆ(w/r_en)Ż¼░┤šš│╠ą“įO(sh©©)Č©Ą─═©ą┼ģf(xi©”)ūh┼cFIFOųąŠÅ┤µĄ─öĄ(sh©┤)ō■(j©┤)═©ą┼Ż¼īŹ(sh©¬)¼F(xi©żn)öĄ(sh©┤)ō■(j©┤)é„▌ö║═ūg┤a’@╩ŠĪŻŽĄĮy(t©»ng)Įė┐┌─ŻēKĄ─▀BĮėĘĮ╩Į╚ńłD3╦∙╩ŠĪŻ

3 ŽĄĮy(t©»ng)▄ø╝■įO(sh©©)ėŗ(j©¼)

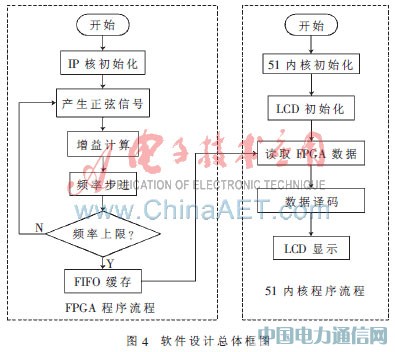

ŽĄĮy(t©»ng)▄ø╝■įO(sh©©)ėŗ(j©¼)ų„ę¬═Ļ│╔ī”(du©¼)š²Žę▓ķšę▒ĒIP║╦Ą─│§╩╝╗»ĪóĘÕųĄÖz▓©│╠ą“Ą─įO(sh©©)ėŗ(j©¼)Īó«É▓ĮFIFOįO(sh©©)ėŗ(j©¼)ĪóFPGA┼c«É▓ĮFIFOĄ─═©ą┼ģf(xi©”)ūhįO(sh©©)ėŗ(j©¼)ęį╝░═¼▓Į’@╩ŠĄ╚å¢Ņ}ĪŻ▄ø╝■įO(sh©©)ėŗ(j©¼)┐é¾w┐“łD╚ńłD4╦∙╩ŠĪŻ

3.1 51ā╚(n©©i)║╦Ą─│§╩╝╗»┼õų├

51ā╚(n©©i)║╦▓╔ė├═Ļ╚½═¼▓ĮĄ─įO(sh©©)ėŗ(j©¼)ĘĮ░ĖŻ¼į┌Įy(t©»ng)ę╗Ą─Ģr(sh©¬)ńŖą┼╠¢(h©żo)Ž┬┐žųŲ├┐ę╗éĆ(g©©)┤µā”(ch©│)å╬į¬Ą─ūxīæ▓┘ū„ĪŻĖ∙ō■(j©┤)51ā╚(n©©i)║╦╠Ä└Ē╦┘Č╚Ą─ę¬Ū¾Ż¼į┌įO(sh©©)ėŗ(j©¼)ųą╩╣ė├20MHzĄ─Ģr(sh©¬)ńŖŻ¼Ģr(sh©¬)ńŖą┼╠¢(h©żo)═©▀^ŽĄĮy(t©»ng)┐éĢr(sh©¬)ńŖĘųŅlĄ├ĄĮĪŻįO(sh©©)ėŗ(j©¼)ųąŻ¼╩ūŽ╚į┌KeilŠÄ│╠Łh(hu©ón)Š│ųąŠÄūgCšZčį┤·┤aŻ¼įō┤·┤aų„꬞ō(f©┤)ž¤(z©”)LCDĄ─│§╩╝╗»▓óīóFPGA▓╔╝»Ą├ĄĮĄ─īŹ(sh©¬)Ģr(sh©¬)öĄ(sh©┤)ō■(j©┤)▀M(j©¼n)ąąūg┤a║═’@╩ŠĪŻŠÄūg║¾╔·│╔Ą─.hex╬─╝■Įø(j©®ng)ŽÓæ¬(y©®ng)Ą─Ė±╩Į▐D(zhu©Żn)ōQŻ¼╔·│╔FPGAĄ─ROM┘Yį┤┐╔╝ė▌dĄ─.coe╬─╝■ŅÉą═ĪŻ

═©▀^Xilinx╠ß╣®Ą─Core Generator╣żŠ▀Ż¼ī”(du©¼)IP║╦╩╣ė├Ą─DATAĪóXDATA║═CODE╚²ĘN┤µā”(ch©│)ģ^(q©▒)▀M(j©¼n)ąą│§╩╝╗»┼õų├Ż¼┤µā”(ch©│)ģ^(q©▒)Ą─┤¾ąĪįO(sh©©)ų├ę¬ęįCšZčį│╠ą“╦∙Ž¹║─Ą─┤µā”(ch©│)┘Yį┤ęį╝░FPGAā╚(n©©i)▓┐Block Memory┘Yį┤┐éĄ─┤¾ąĪČ°Č©ĪŻ▒ŠŽĄĮy(t©»ng)ųą╦∙ėą┤µā”(ch©│)ģ^(q©▒)Ą─öĄ(sh©┤)ō■(j©┤)īÆČ╚Š∙įO(sh©©)ų├×ķ8╬╗Ż¼ŲõųąĖ„┤µā”(ch©│)ģ^(q©▒)ī”(du©¼)æ¬(y©®ng)Ą─ĄžųĘą┼╠¢(h©żo)īÆČ╚×ķ7╬╗Īó11╬╗║═14╬╗ĪŻīóCODEģ^(q©▒)┼õų├×ķų╗ūx─Ż╩ĮŻ©Read OnlyŻ®Ż¼ė├ė┌┤µĘ┼51ā╚(n©©i)║╦Ą─ųĖ┴Ņ┤·┤aŻ¼▓ó▌d╚ļęčĮø(j©®ng)╔·│╔Ą─.coe╬─╝■ĪŻĮø(j©®ng)ŠC║ŽĪóĘŁūgĪóė│╔õĪó▓╝Šų▓╝ŠĆ║═╔·│╔ŠÄ│╠╬─╝■═Ļ│╔51ā╚(n©©i)║╦Ą─įO(sh©©)ėŗ(j©¼)▀^│╠[3]ĪŻ

į┌51ā╚(n©©i)║╦ųąīŹ(sh©¬)¼F(xi©żn)▓╩Ų┴ę║Š¦Ą─’@╩Š┐žųŲ║═öĄ(sh©┤)ō■(j©┤)ūg┤a’@╩ŠŻ¼┐╔ęį┤¾┤¾£pąĪę“▓╩Ų┴│§╩╝╗»Ģr(sh©¬)ą“Å═(f©┤)ļs║═FPGAį┌╚╦ÖC(j©®)Į╗╗źĮń├µįO(sh©©)ėŗ(j©¼)ųąĄ─▓╗ņ`╗ŅąįȰĦüĒĄ─ļyČ╚[4]ĪŻ═¼Ģr(sh©¬)Ż¼▓╔ė├C┤·┤aī”(du©¼)ę║Š¦Ų┴▀M(j©¼n)ąą▓┘ū„Š▀ėąÅVĘ║Ą─═©ė├ąį║═┐╔öU(ku©░)š╣ąįŻ¼«ö(d©Īng)LCDĄ─ą═╠¢(h©żo)Ė─ūāĢr(sh©¬)Ż¼ų╗ąĶī”(du©¼)│§╩╝╗»┐žųŲūų╔įū„ą▐Ė─Š═┐╔ęįīŹ(sh©¬)¼F(xi©żn)’@╩Š┐žųŲĪŻ

3.2 ĘÕųĄÖz▓©─ŻēK

ŽĄĮy(t©»ng)▓╔ė├▄ø╝■ŠÄ│╠Ą─ĘĮĘ©īŹ(sh©¬)¼F(xi©żn)ĘÕųĄÖz▓©Ą─╣”─▄ĪŻ╩ūŽ╚īóÆ▀Ņlģ^(q©▒)ķgĄ╚ĘųŻ¼ųéĆ(g©©)£y(c©©)┴┐Ą╚Ęų³c(di©Żn)╠ÄĄ─ą┼╠¢(h©żo)ĘÕųĄ▓óīóėŗ(j©¼)╦Ń│÷Ą─į÷ęµ┤µ╚ļFIFOųąŻ¼«ö(d©Īng)ę╗┤╬Æ▀├ĶĮY(ji©”)╩°║¾Š═─▄½@Ą├ŽĄĮy(t©»ng)Ą─Ę∙Ņl╠žąįöĄ(sh©┤)ō■(j©┤)ĪŻ

į┌ī”(du©¼)ą┼╠¢(h©żo)ūŅųĄļŖē║▀M(j©¼n)ąą£y(c©©)┴┐ų«Ū░Ż¼ė╔ė┌ą┼╠¢(h©żo)║▄╚▌ęū╩▄ĄĮĖ╔ö_Ż¼╦∙ęį▓╗┼┼│²ą┼╠¢(h©żo)Ģ■(hu©¼)░l(f©Ī)╔·ČČäė(d©░ng)Ą─┐╔─▄ĪŻ╗∙ė┌▀@éĆ(g©©)įŁę“Ż¼į┌£y(c©©)┴┐Ū░▓╔ė├║åęū×V▓©ī”(du©¼)ą┼╠¢(h©żo)▀M(j©¼n)ąąŲĮ╗¼╠Ä└ĒŻ¼ęį£p╔┘ūŅųĄ£y(c©©)┴┐Ą─š`▓ŅĪŻ▀@└’▓╔ė├╚ĪŠ∙ųĄĄ─ĘĮĘ©ĪŻī”(du©¼)▌ö╚ļą┼╠¢(h©żo)ę└┤╬╚ĪųĄĪó▒Ż┤µŻ¼ą╬│╔ę╗éĆ(g©©)ą┬Ą─ą┼╠¢(h©żo)Ż¼įōą┼╠¢(h©żo)ļŖē║ė╔įŁ▌ö╚ļą┼╠¢(h©żo)Ą─Ū░ā╔éĆ(g©©)Ģr(sh©¬)ńŖ╦∙Ą├ļŖē║║═║¾ā╔éĆ(g©©)Ģr(sh©¬)ńŖ╦∙Ą├ļŖē║ų«║═╚ĪŠ∙ųĄĄ├ĄĮĪŻī”(du©¼)ą┼╠¢(h©żo)▀M(j©¼n)ąą║åęūŲĮ╗¼╠Ä└Ē║¾Ż¼╦∙«a(ch©Żn)╔·Ą─ą┬ą┼╠¢(h©żo)ū„×ķūŅųĄ£y(c©©)┴┐Ą─╗∙£╩(zh©│n)ą┼╠¢(h©żo)ĪŻą┼╠¢(h©żo)š¹ą╬║¾Ą├ĄĮś╦(bi©Īo)£╩(zh©│n)Ą─ĘĮ▓©ą┼╠¢(h©żo)Ż¼įōą┼╠¢(h©żo)Ą─ę╗éĆ(g©©)ų▄Ų┌äé║├ī”(du©¼)æ¬(y©®ng)▌ö╚ļą┼╠¢(h©żo)Ą─ā╔éĆ(g©©)ų▄Ų┌Ż¼ŲõųąĖ▀ļŖŲĮ║═Ą═ļŖŲĮĖ„ī”(du©¼)æ¬(y©®ng)ę╗éĆ(g©©)ų▄Ų┌ĪŻ

ą┼╠¢(h©żo)ļŖē║Ą─ĘÕĘÕųĄ╝┤×ķūŅ┤¾ųĄ£p╚źūŅąĪųĄĪŻĄ½╩ŪŻ¼ą┼╠¢(h©żo)Įø(j©®ng)▀^A/D▐D(zhu©Żn)ōQŲ„┴┐╗»ęį║¾Ż¼╦∙Ą├ĄĮĄ─ųĄ×ķ12╬╗Ų½┤aŻ¼öU(ku©░)š╣│╔×ķ16╬╗Ų½┤aŻ¼“1111111111111111”▒Ē╩ŠļŖē║×ķ2VŻ¼“1000000000000000”▒Ē╩ŠļŖē║×ķ0VŻ¼“0000000000000000”▒Ē╩ŠļŖē║×ķŻŁ2VĪŻ╚ń╣¹ų▒ĮėīóūŅ┤¾ųĄ║═ūŅąĪųĄĄ─Ų½┤aŽÓ£pŻ¼ĮY(ji©”)╣¹Ģ■(hu©¼)│÷¼F(xi©żn)Õe(cu©░)š`ĪŻę“┤╦▓╔ė├Ž╚īóūŅąĪųĄŻ©ļŖē║žō(f©┤)ųĄŻ®ūā?y©Łu)ķŽÓæ?y©®ng)Ą─ļŖē║š²ųĄĄ─ĘĮĘ©Ż¼╝┤Ż║ ŲõųąB▒Ē╩ŠūŅąĪųĄŻ¼A▒Ē╩ŠŽÓæ¬(y©®ng)Ą─ļŖē║š²ųĄŻ¼╚╗║¾į┘īóŽÓæ¬(y©®ng)Ą─ļŖē║š²ųĄ┼cūŅ┤¾ųĄŽÓ╝ėŻ¼╝┤×ķą┼╠¢(h©żo)ļŖē║Ą─ĘÕĘÕųĄĪŻ

ŲõųąB▒Ē╩ŠūŅąĪųĄŻ¼A▒Ē╩ŠŽÓæ¬(y©®ng)Ą─ļŖē║š²ųĄŻ¼╚╗║¾į┘īóŽÓæ¬(y©®ng)Ą─ļŖē║š²ųĄ┼cūŅ┤¾ųĄŽÓ╝ėŻ¼╝┤×ķą┼╠¢(h©żo)ļŖē║Ą─ĘÕĘÕųĄĪŻ

3.3 «É▓ĮFIFOįO(sh©©)ėŗ(j©¼)

A/D▓╔╝»öĄ(sh©┤)ō■(j©┤)Ą─öĄ(sh©┤)ō■(j©┤)┬╩║▄Ė▀Ż¼▒Š╬─ųąŽĄĮy(t©»ng)Ģr(sh©¬)ńŖ×ķ40MHzŻ¼▓╔╝»öĄ(sh©┤)ō■(j©┤)īÆČ╚×ķ12╬╗Ż¼▀@śė├┐├ļ▓╔╝»Ą─öĄ(sh©┤)ō■(j©┤)┴┐×ķ40M×12bit/8=60MB/sŻ¼╚ń┤╦Ė▀╦┘Ą─öĄ(sh©┤)ō■(j©┤)┴„▀h(yu©Żn)▀h(yu©Żn)│¼│÷┴╦51ā╚(n©©i)║╦Ą─╠Ä└Ē─▄┴”ĪŻ×ķ▒ŻūC51ā╚(n©©i)║╦ūx╚ĪöĄ(sh©┤)ō■(j©┤)Ą─ėąą¦ąį║═┐╔┐┐ąįŻ¼ŽĄĮy(t©»ng)ųą╩╣ė├«É▓ĮFIFOī”(du©¼)öĄ(sh©┤)ō■(j©┤)▀M(j©¼n)ąąŠÅ┤µĪŻFIFOĄ─įO(sh©©)ėŗ(j©¼)╩Ū═©▀^┼õų├FPGAā╚(n©©i)▓┐Ą─Block RAM┘Yį┤īŹ(sh©¬)¼F(xi©żn)Ą─[5Ż¼6]ĪŻ×ķ┴╦īŹ(sh©¬)¼F(xi©żn)▀ģ▓╔╝»▀ģ’@╩ŠĄ──┐Ą─Ż¼┼õų├ā╔ēKŽÓ═¼Ą─FIFOŻ¼┤¾ąĪŠ∙×ķ512×8bitĪŻį┌ūxīæĢr(sh©¬)ńŖĄ─┐žųŲŽ┬Ż¼═©▀^ūx╩╣─▄║═īæ╩╣─▄ą┼╠¢(h©żo)Ą─įO(sh©©)ų├Ż¼╩╣Ą├į┌═¼ę╗Ģr(sh©¬)┐╠╩╝ĮKėąę╗ēKFIFOį┌▀M(j©¼n)ąąīæ▓┘ū„Ż¼Č°┴Ēę╗ēKFIFOīóīæØMĄ─öĄ(sh©┤)ō■(j©┤)ūx│÷ĪŻī”(du©¼)ė┌═¼ę╗ēKFIFO▓╗į╩įSūxīæą┼╠¢(h©żo)═¼Ģr(sh©¬)ėąą¦Ż¼▀@śėĮė╩š║═ūx╚ĪA/DöĄ(sh©┤)ō■(j©┤)▓óĮ╗Įo51ā╚(n©©i)║╦╠Ä└Ē┐╔ęį═¼Ģr(sh©¬)▀M(j©¼n)ąąŻ¼Å─Č°▒ŻūCöĄ(sh©┤)ō■(j©┤)é„▌ö?sh©┤)─▀B└m(x©┤)ąįĪŻ

4 ŽĄĮy(t©»ng)š{(di©żo)įć║═£y(c©©)įć

į┌═Ļ│╔┴╦ŽĄĮy(t©»ng)Ą─ė▓╝■║═▄ø╝■įO(sh©©)ėŗ(j©¼)ęį║¾Ż¼ąĶę¬▀M(j©¼n)ąąš{(di©żo)įć║═£y(c©©)įćĪŻį┌£y(c©©)įćĢr(sh©¬)Ż¼╩╣ė├ę╗ļALCĄ══©×V▓©ŠW(w©Żng)Įj(lu©░)Ż¼Å─╦∙Ą├ĄĮĄ─Ņl┬╩╠žąįŪ·ŠĆ┐╔ęį┐┤│÷Ż¼ŽĄĮy(t©»ng)ų„Įń├µ’@╩ŠĘĆ(w©¦n)Č©Ż¼Ņü╔½ą┼ŽóžSĖ╗ĪŻ«ö(d©Īng)ŪąōQĄĮŽĄĮy(t©»ng)ĀŅæB(t©żi)įO(sh©©)ų├╗“£y(c©©)įćą┼Žó’@╩ŠĮń├µĢr(sh©¬)Ż¼┐╔ęįī”(du©¼)╝żäŅ(l©¼)ą┼╠¢(h©żo)Ą─Æ▀ŅlĘČć·Īó▓Į▀M(j©¼n)ųĄĪóÆ▀├ĶĢr(sh©¬)ķgĄ╚ģóöĄ(sh©┤)▀M(j©¼n)ąąįO(sh©©)ų├Ż¼═¼Ģr(sh©¬)▀Ć┐╔ęį═©▀^░┤µI▌ö╚ļŅl³c(di©Żn)Ą─ĘĮ╩Į▓ķįāĖ„Ņl³c(di©Żn)ī”(du©¼)æ¬(y©®ng)Ą─į÷굯¼ŪęŠ▀ėą▌^Ė▀Ą─£y(c©©)įćŠ½Č╚ĪŻ

ŽĄĮy(t©»ng)īŹ(sh©¬)¼F(xi©żn)┴╦į┌FPGA║═51ā╚(n©©i)║╦Ą─ŲĮ┼_(t©ói)Ž┬▀M(j©¼n)ąą▒Ńöy╩ĮĘ∙Ņl╠žąį£y(c©©)įćāxĄ─┐é¾wįO(sh©©)ėŗ(j©¼)ĪŻī”(du©¼)įO(sh©©)ėŗ(j©¼)ųąĄ─║╦ą──ŻēK▀M(j©¼n)ąąš{(di©żo)įćŻ¼╚ń51ā╚(n©©i)║╦ĪóTFT-LCDę║Š¦Īó«É▓ĮFIFOĄ╚ĪŻ£y(c©©)įć▒Ē├„Ż¼ŽĄĮy(t©»ng)╣żū„ĘĆ(w©¦n)Č©Īó£y(c©©)┴┐Š½Č╚Ė▀ĪóīŹ(sh©¬)Ģr(sh©¬)ąįÅŖ(qi©óng)Ż¼Ūęė▓╝■ļŖ┬ĘĮY(ji©”)śŗ(g©░u)║åå╬ĪŻ─┐Ū░ŽĄĮy(t©»ng)ęčĮø(j©®ng)æ¬(y©®ng)ė├ĄĮ─│ą═ūāē║Ų„└@ĮMĄ─Ę∙Ņl╠žąį£y(c©©)įćųąŻ¼▓ó╚ĪĄ├┴╦┴╝║├Ą─£y(c©©)į湦╣¹ĪŻ▒Š╬─┤“ŲŲ┴╦ęįĢr(sh©¬)ą“Ę┬šµ║═╣”─▄“×(y©żn)ūC×ķ─┐Ą─Ą─51ā╚(n©©i)║╦蹊┐Ż¼īó51ā╚(n©©i)║╦║Ž└Ēæ¬(y©®ng)ė├ĄĮļŖūėŽĄĮy(t©»ng)įO(sh©©)ėŗ(j©¼)īŹ(sh©¬)└²ųąŻ¼▓ó╚ĪĄ├┴╦│╔╣”Ż¼ī”(du©¼)ė┌ęį║¾Ė³╝ėÅ═(f©┤)ļsĄ─ļŖūėŽĄĮy(t©»ng)įO(sh©©)ėŗ(j©¼)╠ß╣®┴╦ģó┐╝║═ę└ō■(j©┤)ĪŻ