š¬ę¬Ż║æ¬IEEE1394═¼╣Ō└w═©Ą└┐éŠĆĄ─╗ź┬ōąĶŪ¾Ż¼įOėŗ┴╦ę╗ĘN╗∙ė┌╣Ō└w═©Ą└Ą─IEEE1394╣Ōą┼╠¢é„▌öŽĄĮyĪŻįōŽĄĮyęį╗∙ė┌¼Fł÷┐╔ŠÄ│╠▀ē▌ŗĻć┴ą(FPGA)įOėŗĄ─ģfūhė│╔õ─ŻēK×ķ║╦ą─Ż¼īŹ¼F┴╦īóIEEE1394ą┼╠¢═©▀^╣Ō└w═©Ą└▀Mąąé„▌öĄ─╣”─▄ĪŻĘ┬šµĮY╣¹▒Ē├„Ż¼įōŽĄĮy─▄▀_ĄĮ1.0625Gb/sĄ─╣żū„╦┘┬╩ĪŻ

║Į┐šļŖūėŽĄĮyĮø▀^Äū╩«─ĻĄ─░lš╣Ż¼š²į┌ĮøÜvÅ──ŻöM╗»Ž“öĄūų╗»ŽĄĮyĄ─▐DūāŻ¼ų▓Į┐ń╚ļĄ┌4┤·║Į┐šļŖūėŽĄĮyŻ¼Ųõų„ę¬╠ž³cŠ═╩Ūį┌Ą┌3┤·╗∙ĄA╔ŽŻ¼ęįĖ▀╦┘┤¾╚▌┴┐Ą─ą┼ŽóĮ╗ōQ×ķ╗∙ĄAŻ¼Å─ŠC║Ž╗»Ž“Ė▀Č╚ŠC║Ž╗»░lš╣Ż¼īŹ¼F┘Yį┤╣▓ŽĒ┼cöĄō■╚┌║ŽŻ¼Ųõ╚╬äšäØĘųĪó─ŻēKĘų┼õ║═ū„śIš{Č╚Ż¼Č╝ę└┘ćė┌öĄō■ŠWĮjŽĄĮyĄ─ąį─▄Ż¼▀@ą®ąį─▄░³└©ŠWĮj═žōõĮYśŗĪóé„▌öĦīÆĪó┐╔┐┐ąį╝░öĄō■čė▀tąį─▄Ą╚ĪŻę“┤╦Ż¼╬┤üĒŽ╚▀M║Į┐šļŖūėŽĄĮyųąĖ„šŠ³cų«ķgĄ─öĄō■┴„īóĖ³×ķÅ═ļsŻ¼░³└©╔õŅlĪóęĢŅlĄ╚┤¾┴„┴┐öĄō■Ż¼ėąĄ─╣سc╦┘┬╩ąĶŪ¾īó│¼▀^1Gb/sŻ¼Č°¼FėąĄ─Ą═╦┘öĄō■┐éŠĆ║▄ļyØMūŃ╚ń┤╦Ė▀╦┘Ą─öĄō■é„▌öę¬Ū¾ĪŻ

├└ć°ć°╝ęś╦£╩╬»åTĢ■ė┌1988─Ļķ_╩╝ųŲČ©Ą─╣Ō└w═©Ą└(Fiber ChannelŻ¼FC)╩Ūę╗ĘNĖ▀╦┘┤«ąą┐éŠĆģfūhŻ¼▓╗āHŠ▀ėąĖ▀ĦīÆĪóĖ▀┐╔┐┐ąįĪóĄ═čėĢrĪóé„▌öŠÓļx▀hĪó═žōõņ`╗ŅĄ─ā׳cŻ¼Č°Ūęų¦│ųČÓĘN╔Žīėé„▌öģfūhĪŻ╣Ō└w═©Ą└Ą─▀@ę╗ā׳c╩╣Ą├į┌═¼ę╗╬’└ĒĮė┐┌╔Ž▀\ąąČÓĘN╔Žīė═©Ą└ś╦£╩║═ŠWĮjģfūh│╔×ķ┐╔─▄ĪŻ─┐Ū░ęčĮøīŹ¼FĄ─ML-STD-1553ĄĮ╣Ō└w═©Ą└ģfūhĄ─ė│╔õŻ¼ęį╝░ML-STD-1553▀h│╠ĮKČ╦Ų„╝■┼c╣Ō└w═©Ą└╗ź┬ōĘĮ░ĖĄ─ŽĄĮyŠC║ŽŻ¼×ķ╬┤üĒ║Į┐šļŖūėŽĄĮyųą▓╗═¼┐éŠĆĄ─╗ź▀B╠ß╣®┴╦ę╗Ślą┬Ą─═ŠÅĮŻ¼╩╣Ą├ŽĄĮyį┌▒Ż┴¶é„ĮyŠWĮj═žōõ║═ģfūhĄ─═¼ĢrŻ¼½@Ą├╣Ō└w═©Ą└╦∙╠ß╣®Ą─Ė▀ĦīÆĘ■äšĪŻ

╗∙ė┌┤╦įOėŗ╦╝ŽļŻ¼▒Š╬─╠ß│÷┴╦ę╗ĘNIEEE1394ĄĮ╣Ō└w═©Ą└é„▌öģfūhĄ─ė│╔õĘĮ░ĖŻ¼į┌┤╦╣żū„╗∙ĄA╔ŽŻ¼└¹ė├¼Fł÷┐╔ŠÄ│╠▀ē▌ŗĻć┴ą(FPGA)Ż¼ī”╦∙╠ß│÷Ą─ģfūhė│╔õĘĮ░Ė▀Mąą┴╦ė▓╝■įOėŗ┼cīŹ¼FŻ¼įOėŗ┴╦ę╗éĆ╗∙ė┌FCĄ─IEEE1394╣Ōą┼╠¢é„▌öŽĄĮyĪŻ

1 IEEE1394ĄĮ╣Ō└w═©Ą└Ą─ģfūhė│╔õ

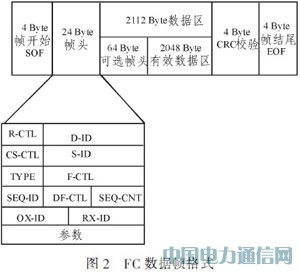

╩ūŽ╚║åę¬ĮķĮB▒Š╬─╠ß│÷Ą─ę╗ĘNIEEE1394ĄĮ╣Ō└w═©Ą└é„▌öģfūhĄ─ė│╔õĘĮ░ĖŻ¼Ė³įö╝ÜĄ─šf├„┐╔ģó┐╝╬─½IĪŻ╦∙╠ßģfūhė│╔õĘĮ░ĖĄ─╗∙▒Š╦╝Žļ╩ŪŻ║į┌IEEE1394ĄĮFCöĄō■░³Ą─ė│╔õ▀^│╠ųąŻ¼▒Ż┴¶FCįŁüĒĄ─ļĖ±╩Įą╬╩ĮŻ¼īóFCļŅ^▓┐Ęųųąį┤╣سc║═─┐Ą─╣سcĄ─ĄžųĘĘųäeė│╔õ×ķIEEE1394į┤╣سc║═─┐Ą─╣سcĄ─ĄžųĘŻ¼▓óīóIEEE1394öĄō■░³ųą│²┴╦öĄō■ė“═ŌĄ─Ųõ╦¹ą┼Žóė│╔õĄĮFCĄ─64Byte┐╔▀xļŅ^╔ŽŻ¼öĄō■ė“Ą─ą┼Žóė│╔õĄĮFCĄ─ėąą¦öĄō■ģ^ĪŻ┤╦═ŌŻ¼ė╔ė┌FCę╗éĆöĄō■ļĄ─ėąą¦öĄō■ģ^ķLČ╚ų╗ėą2048ByteŻ¼Č°į┌═©Ą└é„▌ö╦┘┬╩┤¾ė┌200Mb/sŻ¼IEEE1394Ą─Ą╚ĢröĄō■░³╗“é„▌ö╦┘┬╩┤¾ė┌400Mb/sĢrŻ¼«É▓ĮöĄō■░³Ą─ūŅ┤¾ėąą¦ķLČ╚īó│¼│÷FCėąą¦öĄō■ģ^Ą─┤¾ąĪĪŻę“┤╦Ż¼«öIEEE1394öĄō■░³Ą─ķLČ╚│¼│÷┴╦FCėąą¦öĄō■ģ^ķLČ╚ĢrŻ¼æ¬įōīóįōöĄō■░³ė│╔õ│╔ę╗éĆ▀B└mĄ─FCöĄō■ļą“┴ąĪŻŽ┬├µęįIEEE1394«É▓ĮöĄō■░³ĄĮFCöĄō■ļĄ─ė│╔õ×ķ└²Ż¼šf├„ā╔ĘNģfūhĄ─ė│╔õ▀^│╠ĪŻ

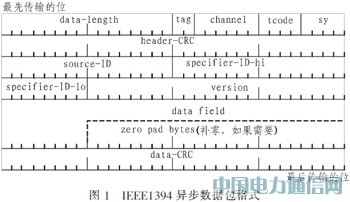

IEEE1394«É▓ĮöĄō■░³╝░FCöĄō■ļĖ±╩Į╚ńłD1Ż¼łD2╦∙╩ŠĪŻłD3×ķIEEE1394öĄō■ļĄĮ╣Ō└w═©Ą└ļĖ±╩Įė│╔õĻPŽĄĪŻ

ī”ė│╔õ▀^│╠Ą─šf├„Ż║

1)─┐Ą─╣سc║═į┤╣سcĄžųĘė╔IEEE1394Ą─16╬╗öU│õĄĮ24╬╗Ż¼╩╣ŠWĮjęÄ─ŻūāĄ├▒╚å╬ę╗Ą─IEEE1394ŠWĮję¬┤¾ĪŻ

2)T-TYPEė├üĒųĖ├„Į╗ōQŽ¹ŽóĄ─é„▌ö╠žąįŻ¼░³└©Į╗ōQĄ─é„▌öĘĮŽ“║═ĮKČ╦-ĮKČ╦(NT-NT)Į╗ōQĄ─ąį─▄Č©┴xĪŻį┌NT-NTŅÉą═Į╗ōQųąŻ¼īó×ķĮė╩šNT╠ß╣®░l╦═NTĄ─ĄžųĘŻ¼╗“š▀×ķ░l╦═NT╠ß╣®Įė╩šNTĄ─ĄžųĘĪŻ

3)T—CTLė├ė┌īŹ¼FFCŠWĮj║═IEEE1394ŠWĮjų«ķgĄ─Ž¹Žóé„▌öŻ¼īŹ¼Fā╔š▀ų«ķgĄ─ś“┬Ę▀BĮėŻ¼═Ļ│╔FCŠWĮjĮKČ╦╗“ŠWĮj┐žųŲŲ„┼cIEEE1394╣سcų«ķgĄ─Ž¹Žóé„▌öĪŻ

4)īóIEEE1394ųąĄ─ļŅ^CRCąŻ“×║═öĄō■CRCąŻ“×Ęųķ_ĪŻį┌IEEE1394öĄō■é„▌öųąŻ¼╩ūŽ╚▀MąąĄ─╩ŪļŅ^CRCąŻ“ׯ¼╚ń╣¹░l¼FÕeš`Ż¼ät┴ó╝┤ÆüŚēįōļĪŻ╦∙ęį▀@└’įOŽļīóIEEE1394öĄō■CRCĘ┼į┌╣Ō└w═©Ą└öĄō■ļĄ─┐╔▀xļŅ^Ż¼īóļŅ^CRCĘ┼į┌╣Ō└w═©Ą└öĄō■ļCRCąŻ“×ųąŻ¼▀@śė┐╔ęįŽ╚Öz£yļŅ^CRCŻ¼╣Ø╩ĪŽĄĮyķ_õNĪŻ

2 IEEE1394╣Ōą┼╠¢é„▌öŽĄĮyįOėŗ┼cīŹ¼F

2.1 ŽĄĮyĄ─śŗ╝▄

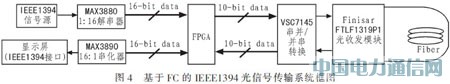

×ķį┌╣Ō└w═©Ą└é„▌öIEEE1394ą┼╠¢Ż¼śŗĮ©ā╔ĘN┐éŠĆ╗ź▀BĄ─ė▓╝■ŲĮ┼_Ż¼╦∙įOėŗĄ─é„▌öŽĄĮy▓╗āHę¬īŹ¼Fā╔ĘNöĄō■ļĖ±╩ĮĄ─▐DōQŻ¼▀Ćę¬īŹ¼FFC-0ĪóFC-1ĪóFC-2ģfūhīėųąĄ─▓┐Ęų╣”─▄ĪŻ▒Š╬─╦∙įOėŗĄ─╗∙ė┌FCĄ─IEEE1394╣Ōą┼╠¢é„▌öŽĄĮyĮYśŗ╚ńłD4╦∙╩ŠŻ¼░³└©IEEE1394ą┼╠¢į┤Ż¼╗∙ė┌FPGAĄ─1394-FCģfūh▐DōQŲ„Ż¼▒žę¬Ą─═Ōć·Įė┐┌Ų„╝■ęį╝░╣Ō└w╩š░l─ŻēKŻ¼ŽĄĮyé„▌ö╦┘┬╩1.0625Gb/sĪŻŲõųąŻ¼╣Ō└w═©Ą└FC-0īėĄ─╣”─▄ė╔╣ŌļŖ▐DōQ─ŻēK║═┤«▓ó┼c▓ó┤«▐DōQąŠŲ¼īŹ¼FŻ¼Č°IEEE1394ĄĮFCöĄō■ļė│╔õ╝░FC-1ĪóFC-2īė╣”─▄ų„ę¬╗∙ė┌FPGA▀Mąąė▓╝■ŠÄ│╠üĒīŹ¼FĪŻ

2.2 ╗∙ė┌FPGAĄ─╣”─▄─ŻēKįOėŗ┼cīŹ¼F

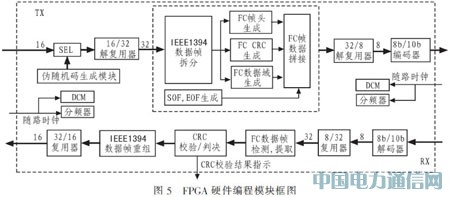

į┌╦∙įOėŗĄ─ŽĄĮyųąŻ¼FPGAų„ę¬īŹ¼FIEEE1394ĄĮFCĄ─öĄō■ļė│╔õęį╝░FC-1ĪóFC-2īė╣”─▄ĪŻ╗∙ė┌FPGAĄ─╣”─▄─ŻēKĮYśŗ╚ńłD5╦∙╩ŠĪŻ

1)FC-1īė╣”─▄å╬į¬░³└©8b/10bŠÄ┤a/ĮŌ┤a─ŻēK║═D/KŅÉą═ųĖ╩Š─ŻēKĪŻ

2)FC-2īė╣”─▄å╬į¬░³└©öĄō■Įė╩š─ŻēKŻ¼░l╦═─ŻēK╝░ŽĄĮy┼õų├─ŻēKĪŻ

3)IEEE1394ĄĮFCĄ─öĄō■ļė│╔õ─ŻēK(ģfūh▐DōQ)╩ŪFPGAįOėŗĄ─║╦ą─▓┐ĘųĪŻįō▓┐Ęų─▄ē“═Ļ│╔ī”ą┼╠¢į┤░l│÷Ą─IEEE1394öĄō■ļĄĮFCģfūhĄ─öĄō■ļĄ─ė│╔õ╣żū„Ż¼╝┤īóIEEE1394öĄō■ļ▐DōQ×ķFCļĖ±╩ĮĪŻ═¼Ģr─▄Å─Įė╩šĄĮĄ─FCöĄō■ļ▀ĆįŁ│÷IEEE1394öĄō■ļĪŻ

4)FPGAŲ¼ā╚Ą─░l╦═(TX)▓┐Ęų║═Įė╩š(RX)▓┐ĘųŠ∙╝ė╚ļ┴╦öĄūųĢrńŖ╣▄└Ē(DCM)║═ĘųŅlŲ„─ŻēKŻ¼DCM┐╔ęį╩╣ĢrńŖą┼╠¢═©▀^ĢrńŖśõ▀_ĄĮĖ„éĆŲ¼ā╚╝─┤µŲ„Ż¼ęį£pąĪŲ¼ā╚ĢrńŖą┼╠¢Ą─ČČäė║═čėĢrŻ¼╠ßĖ▀ŽĄĮy▀\ąą╦┘┬╩ĪŻ

┤╦═ŌŻ¼×ķ┴╦ĘĮ▒Ńį┌ø]ėą═ŌĮėIEEE1394ą┼╠¢į┤Ą─ŪķørŽ┬ī”FPGAā╚▓┐Ą─╣”─▄─ŻēK▀Mąąš{įćŻ¼į┌FPGAĄ─TXŪ░═©▀^▓╔ė├ŠĆąįĘ┤üęŲ╬╗╝─┤µŲ„IP║╦śŗĮ©┴╦ę╗éĆé╬ļSÖCą“┴ą░l╔·Ų„Ż¼┐╔ęįė├üĒ─ŻöMIEEE1394öĄō■į┤Ż¼▓ó═©▀^1éĆČ■▀xę╗▀xō±Ų„īŹ¼F═Ō▓┐▌ö╚ļą┼╠¢┼cā╚▓┐é╬ļSÖCą“┴ąĄ─▀xō±╣”─▄ĪŻ

FPGAā╚▓┐Ą─╣żū„▀^│╠šf├„╚ńŽ┬Ż║IEEE1394öĄō■Å─16:32ĮŌÅ═ė├Ų„▌ö│÷ų«║¾Ż¼▀M╚ļIEEE1394öĄō■▓Ęų─ŻēKŻ¼«a╔·ī”æ¬ė┌FCöĄō■ļĄ─SOFĪóDATAĪóCRCĪóEOFĄ─öĄō■Č╬Ż¼╔·│╔Ę¹║ŽFCļĖ±╩ĮĄ─öĄō■ĪŻį┌▀@ų«║¾Ż¼32:8Å═ė├─ŻēKīó32bit▓óąą▌ö╚ļĄ─öĄō■Å═ė├│╔8bit▓óąą▌ö│÷Ą─öĄō■ĪŻļS║¾▀M╚ļ8b/10bŠÄ┤a─ŻēKŻ¼═Ļ│╔8b/10bĄ─ŠÄ┤a╣żū„▓óęį10bit╬╗īÆŻ¼106.25MHzĄ─╦┘┬╩╦═╚ļVSC7145┤«▓ó/▓ó┤«ąŠŲ¼Ż¼ūŅ║¾ęį1.0625GbsĄ─╦┘┬╩▌ö│÷ĄĮSFP╣Ō╩š░l─ŻēKŻ¼ė╔╣Ō╩š░l─ŻēKīóļŖą┼╠¢š{ųŲ│╔╣Ōą┼╠¢▌ö│÷ĪŻ

į┌RXĮė╩š▓┐ĘųŻ¼ė╔╣Ō╩š░l─ŻēK▀ĆįŁ│╔Ą─ļŖą┼╠¢═©▀^VSC7145┤«▓ó/▓ó┤«ąŠŲ¼║¾ęį10bitĄ─▓óąąöĄō■ą╬╩Į▌ö╚ļĄĮFPGAųąŻ¼ė╔8b/10bĮŌ┤aŲ„ĮŌ┤aŻ¼▌ö│÷8bit▓óąąöĄō■(į┌ĮŌ┤a▀^│╠ųąŻ¼ĮŌ┤aŲ„┐╔ęį═©▀^┼ąöÓ┤a┴„Ą─śOąįüĒ┼ąäe╩Ūʱį┌é„▌ö▀^│╠ųą│÷¼Fš`┤a)ĪŻ8b/10bĮŌ┤a▌ö│÷║¾Ą─öĄō■═©▀^1éĆ8:32ĮŌÅ═ė├─ŻēKĮŌÅ═ė├│╔32bitĄ─▓óąąöĄō■Ż¼▓óąąų¦┬Ę╦┘┬╩×ķ26.5625MHzŻ¼ļS║¾32╬╗▓óąąöĄō■═©▀^FCļÖz£y╠ß╚Ī─ŻēKŻ¼╔·│╔ś╦ūRą┼╠¢ļS┬Ę▌ö│÷ĪŻį┌CRCąŻ“×/┼ąøQ─ŻēKųąŻ¼öĄō■═©▀^CRC╬╗▀\╦ŃĘ┤ė│╩Ūʱ│÷¼Fš`┤aŻ¼▓óĮo│÷ųĖ╩ŠĪŻį┌▀@ų«║¾Ż¼FCöĄō■ļųžĮM×ķIEEE1394öĄō■ļŻ¼ūŅ║¾Įøė╔32:16Å═ė├─ŻēKīó32bit▓óąąIEEE1394ļöĄō■ųžą┬Å═ė├│╔16bit▓óąąöĄō■Ż¼┼c53.12MHzĄ─ļS┬Ęą┼╠¢ę╗═¼╦═│÷FPGAąŠŲ¼ĪŻ

3 FPGA╣”─▄“×ūC

▒ŠįOėŗęčį┌Xilinx Spartan3ŽĄ┴ąĄ─Xc3s200ųąīŹ¼FŻ¼▓óį┌Xilinx ISE 7.1Ę┬šµŁhŠ│Ž┬▀Mąą┴╦╣”─▄║═Ģrą“Ę┬šµ“×ūCĪŻ▓╔ė├é╬ļSÖCą“┴ą░l╔·Ų„╔·│╔Ą─é╬ļSÖC┤·┤a─ŻöMIEEE1394öĄō■į┤Ż¼įOČ©├┐1000Byte×ķę╗éĆöĄō■░³░³ķLĪŻ

3.1 ╣”─▄Ę┬šµĮY╣¹

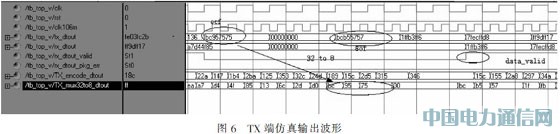

1)į┌░l╦═Č╦Ż¼IEEE1394öĄō■░³▒╗▓ĘŌŻ¼ųžĮM│╔FCöĄō■ļŻ¼▓óė╔8b/10bŠÄ┤aŲ„ŠÄ┤a║¾▌ö│÷Ż¼╚ńłD6ųąĘ┬šµ▓©ą╬tx_dtoutŻ¼║═TX_encode_ dtout╦∙╩ŠĪŻ

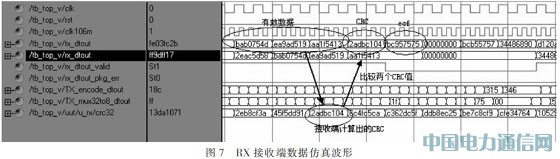

2)į┌Įė╩šČ╦Ż¼FCļĮYśŗ▒╗š²┤_Öz£y▓ó╠ß╚ĪŻ¼į┌CRCąŻ“ך²┤_║¾ųžĮM│╔IEEE1394öĄō■ļĖ±╩Į▌ö│÷Ż¼╚ńłD7ųąĘ┬šµ▓©ą╬tx_dtoutŻ¼crc32╝░rx_dtout╦∙╩ŠĪŻ

ĮøĘ┬šµ£yįćŻ¼FPGAīŹ¼FIEEE1394ĄĮFCöĄō■ļĖ±╩ĮĄ─ė│╔õ╣”─▄Ż¼Ė„─ŻēKŠ∙š²│Ż╣żū„Ż¼öĄō■═©ą┼┴╝║├Ż¼¤oüG░³¼FŽ¾ĪŻ

3.2 Ģrą“Ę┬šµĮY╣¹

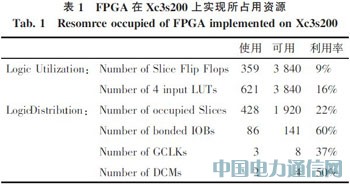

įōįOėŗį┌Xc3s200╔ŽīŹ¼F║¾Ż¼FPGA╦∙╩╣ė├Ą─┘Yį┤╚ń▒Ē1╦∙╩ŠŻ¼š¹éĆŽĄĮy┘Yį┤š╝ė├┬╩▌^Ą═Ż¼ūŅĖ▀▀\ąą╦┘┬╩─▄▀_ĄĮ135.245MHzŻ¼ØMūŃ106.25MHzĄ─Ų¼╔ŽūŅĖ▀▀\ąą╦┘┬╩ę¬Ū¾Ż¼įOėŗ▀_ĄĮ┴╦ŅAŲ┌ĮY╣¹ĪŻ

4 ĮY╩°šZ

╣Ō└w═©Ą└Š▀ėąų¦│ųČÓĘN╔Žīėé„▌öģfūhĄ─ā׳cŻ¼▒Š╬─į┌ęčėą╣żū„Ą─╗∙ĄA╔ŽŻ¼└¹ė├FPAGŻ¼ī”╦∙╠ß│÷Ą─IEEE1394ĄĮ╣Ō└w═©Ą└Ą─ģfūhė│╔õĘĮ░Ė▀Mąą┴╦ė▓╝■įOėŗŻ¼═©▀^FPGA╣”─▄Ę┬šµ╝░Ģrą“Ę┬šµ“×ūC┴╦╦∙╠ßĘĮ░ĖĄ─┐╔ąąąįĪŻ└¹ė├┤╦FPGAģfūh▐DōQ─ŻēKŻ¼▒Š╬─▀ĆįOėŗ┴╦╗∙ė┌FCĄ─IEEE1394╣Ōą┼╠¢é„▌öŽĄĮyŻ¼Įo│÷┴╦Š▀¾wĄ─ė▓╝■įOėŗĘĮ░ĖĪŻ─┐Ū░Ż¼┤╦ŽĄĮyĄ─ų„꬚{įć╣żū„ęč═Ļ│╔Ż¼║¾└mĄ─╣żū„īó═©▀^ŽĄĮyé„▌öīŹ“ׯ¼ī”ŽĄĮyąį─▄▀MąąĘų╬÷蹊┐ĪŻ