ėŗ║═Ģrą“Ę┬šµŻ¼ė▓╝■▓┐Ęųį┌Altera ╣½╦Š EP2C15AF256C8N FPGA ╔ŽīŹ¼FĪŻĮY╣¹▒Ē├„Ż¼öĄūųMSKš{ųŲĮŌš{Ų„Š▀ėąŽÓ╬╗▀B└mŻ¼ŅlĦ└¹ė├┬╩Ė▀Ą─ā׳cĪŻ

öĄūųš{ųŲĮŌš{Ų„į┌³cī”³cĄ─öĄō■é„▌öųąĄ├ĄĮ┴╦ÅVĘ║Ą─æ¬ė├ĪŻ═©│ŻĄ─Č■▀MųŲöĄūųš{ųŲĮŌš{Ų„╩ŪĮ©┴óį┌─ŻöM▌d▓©╔ŽĄ─Ż¼į┌ļŖ┬ĘīŹ¼FĢrąĶę¬─ŻöMą┼╠¢į┤Ż¼▀@Ģ■Įo╚½öĄūųæ¬ė├ł÷║ŽÄ¦üĒ▓╗ĘĮ▒ŃĪŻ▒Š╬─Ęų╬÷┴╦MSKŻ©ūŅąĪŅlęŲµI┐žŻ®öĄūųš{ųŲą┼╠¢╠žš„Ż¼╠ß│÷ę╗ĘN╚½öĄūų╣╠Č©öĄō■╦┘┬╩MSKš{ųŲĮŌš{Ų„Ą─įOėŗĘĮĘ©Ż¼æ¬ė├VHDL šZčį▀Mąą┴╦─ŻēKįOėŗ║═Ģrą“Ę┬šµĪŻė▓╝■▓┐Ęųį┌Altera╣½╦Š EP2C15AF256C8N FPGA ╔ŽīŹ¼F┴╦MSK öĄūųš{ųŲĮŌš{Ų„Ż¼▓óį┌│Żų▌╩ą┐Ų╝╝╣źĻPĒŚ─┐Ż║╝ZÄņā”╝Z░▓╚½ŠWĮjųŪ─▄▒O£yŽĄĮyĄ─ŪČ╚ļ╩Į£y┐ž▓┐Ęųæ¬ė├ĪŻīŹ£y▒Ē├„Ż¼öĄūųMSK š{ųŲĮŌš{Ų„Š▀ėą░³Įj║ŃČ©Ż¼ŽÓ╬╗▀B└mŻ¼ŅlĦ└¹ė├┬╩Ė▀Ą─ā׳cĪŻ▓óŪęį┌FPGA ╔ŽīŹ¼FĢrįOėŗą¦┬╩Ė▀Ż¼┐╔┼cŲõ╦¹─ŻēK╣▓ė├Ų¼╔Ž┘Yį┤Ż¼ī”ė┌╚½öĄūųŽĄĮyųąĄ─Č╠ŠÓļxöĄō■═©ą┼╩Ū▌^║├Ą─ĮŌøQĘĮ░ĖĪŻ

1 öĄūųMSK š{ųŲĄ─▌d▓©Ņl┬╩┼cŽÓ╬╗│ŻöĄ

ūŅąĪŅlęŲµI┐žMSK ( Minimum Frequency Shift Keying ) ╩ŪČ■▀MųŲ▀B└mŽÓ╬╗FSK Ą─ę╗ĘN╠ž╩Ōą╬╩ĮĪŻėąĢrę▓ĘQ×ķ┐ņ╦┘ŅlęŲµI┐ž(FFSK)ĪŻMSK š{ųŲĘĮ╩Į─▄ęįūŅąĪĄ─š{ųŲųĖöĄ(0.5)½@Ą├š²Į╗ą┼╠¢Ż¼ ═¼ĢrMSK ▒╚2PSK Ą─öĄō■é„▌ö╦┘┬╩Ė▀Ż¼Ūęį┌Ħ═ŌĄ─ŅlūVĘų┴┐ę¬▒╚2PSK ╦ź£pĖ³┐ņĪŻ

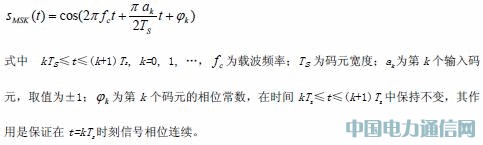

MSK ╩Ū║ŃČ©░³Įj▀B└mŽÓ╬╗Ņl┬╩š{ųŲŻ¼Ųõą┼╠¢Ą─▒Ē╩Š╩Į×ķ

MSK š{ųŲ▒žĒÜ═¼ĢrØMūŃš{ųŲųĖöĄ0.5 ║═ŽÓ╬╗▀B└mŚl╝■Ż¼ė╔MSK ą┼╠¢▒Ē╩Š┐╔ų¬Ż¼×ķ┴╦╩╣š{ųŲųĖöĄ×ķ0.5Ż¼MSK ą┼╠¢Ą─ā╔éĆŅl┬╩æ¬Ęųäe×ķŻ║

╔Ž╩ĮĘ┤ė│┴╦MSK ą┼╠¢Ū░║¾┤aį¬ģ^ķgĄ─╝s╩°ĻPŽĄĪŻMSK ą┼╠¢į┌Ą┌k éĆ┤aį¬Ą─ŽÓ╬╗│ŻöĄ▓╗āH┼c«öŪ░┤aį¬Ą─╚ĪųĄėąĻPŻ¼Č°Ūę▀Ć┼cŪ░ę╗éĆ┤aį¬Ą─╚ĪųĄ╝░ŽÓ╬╗│ŻöĄėąĻPĪŻį┌öĄūų▌d▓©Ą─ŪķørŽ┬Ż¼╔Ž╩÷Śl╝■Ą╚═¼ė┌Ė∙ō■Ū░ę╗┤aį¬Ą─ŽÓ╬╗Ż¼▀xō±«öŪ░┤aį¬Ą─ŽÓ╬╗╩Ū═¼ŽÓ╗“Ę┤ŽÓŻ¼ęį▒ŻūCöĄūųMSKą┼╠¢Ą─ŽÓ╬╗▀B└mĪŻ

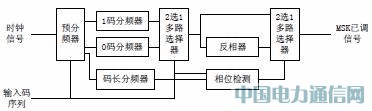

2 öĄūųMSK š{ųŲĮŌš{Ų„FPGA ─ŻēKīŹ¼Fė├FPGA īŹ¼FĄ─MSK š{ųŲŲ„─ŻēK╚ńłD1 ╦∙╩ŠĪŻ

łD1 MSK š{ųŲŲ„─ŻēK

łDųąŅAĘųŅlŲ„║═“0”Īó“1”┤aĘųŅlŲ„ĮM│╔▌d▓©░l╔·Ų„Ż¼į┌▌ö╚ļ┤aą“┴ą═¼▓Įą┼╠¢Ą─┐žųŲŽ┬Ęųäe«a╔·“0”┤a║═“1”┤aĄ─öĄūų▌d▓©ĪŻ×ķ┴╦ĘĮ▒ŃįOėŗ┼cš{š¹Ż¼ŅAĘųŅlŲ„įOų├2 ╝ēĘųŅlļŖ┬ĘŻ¼ĘųŅlŽĄöĄĘųäe×ķD1 ║═D2Ż¼Å─ĘųŅlą¦┬╩┐╝æ]Ż¼D1 ║═D2 Ą─│╦Ęeæ¬×ķ┐éĘųŅlŽĄöĄĄ─ūŅ┤¾╣½╣▓ę“ūėĪŻ

“0”┤a║═“1”┤aĘųŅlŲ„Ą─ĘųŅlŽĄöĄC1ĪóC2 Ą─įOų├▒žĒÜØMūŃš{ųŲųĖöĄ0.5 Ą─Śl╝■ĪŻ▌ö╚ļš{ųŲą┼╠¢öĄūųą“┴ą┐žųŲ2 ▀x1 ČÓ┬Ę▀xō±Ų„Ż¼▀x│÷ī”æ¬▌ö╚ļ┤a┴„ųą“0”Īó“1”┤aį¬Ą─öĄūų▌d▓©ĪŻŽÓ╬╗Öz£y─ŻēK┼cĄ┌Č■╝ē2 ▀x1 ČÓ┬Ę▀xō±Ų„Īó┤aķLĘųŅlŲ„║═Ę┤ŽÓŲ„ĮM│╔▀B└mŽÓ╬╗ą╬│╔ļŖ┬ĘĪŻį┌Ū░├µ┤_Č©“0”Īó“1”┤aį¬Ą─öĄūų▌d▓©ĢrŻ¼├┐éĆ┤aį¬Ą─▌d▓©ų▄Ų┌öĄę▓ļSų«┤_Č©Ż¼ Ųõųą“0”Īó“1”öĄūų▌d▓©ŽÓ╬╗▓Ņ╣╠Č©×ķ180°Ż¼ę“┤╦┐╔ęį║åå╬Ąžė├0Īó1 üĒ▒Ē╩Š2 éĆ▌d▓©ŽÓ╬╗ĪŻį┌ŽÓ╬╗Öz£y─ŻēKųąŻ¼┤aķLĘųŅlŲ„ū„×ķ1bit čėĢrĄ─ĢrńŖą┼╠¢Ż¼▌ö╚ļöĄūųą┼╠¢čė▀tę╗┤aį¬ą┼╠¢D-1 ┼cŪ░┤╬«a╔·Ą─2 ▀x1 ▀xō±Ų„┐žųŲą┼╠¢S ▒╚▌^Ż¼Ą├ĄĮŪ░ę╗┤aį¬ĮY╩°ĢrĄ─ŽÓ╬╗Q-1Ż¼ŲõĮY╣¹╚ń▒Ē1 ╦∙╩ŠĪŻ

łD2 MSK ĮŌš{Ų„─ŻēK

öĄūųMSK ą┼╠¢Ą─ĮŌš{╩Ūė╔┤aį¬═¼▓Į║═┤aą“┴ąÖz£yČ■▓┐ĘųīŹ¼FĄ─ĪŻŅAĘųŅlŲ„Īó“1”┤aĘųŅlŲ„║══¼▓ĮÖz£y─ŻēKĮM│╔┤aį¬═¼▓ĮļŖ┬ĘŻ¼═©▀^ī”▌ö╚ļą┼╠¢ųąĄ─“1”┤aÖz£yĮ©┴ó┤aį¬═¼▓ĮĪŻį┌═¼▓ĮÖz£y─ŻēKųąŻ¼“1”┤aĘųŅlŲ„Ą─═¼ŽÓ║═Ę┤ŽÓ┤a═¼Ģr┼c▌ö╚ļą┼╠¢▒╚▌^Ż¼▓óė╔═¼▓Į┤aķLėŗöĄŲ„ėŗöĄŻ¼«öėŗöĄķLČ╚Ą╚ė┌┤aį¬ķLČ╚Ģr▌ö│÷═¼▓Įą┼╠¢ĪŻ▀M╚ļ┤aį¬═¼▓ĮĀŅæB║¾Ż¼į┌┤aķLĘųŅlŲ„▌ö│÷Ą─┤aį¬═¼▓Įą┼╠¢┐žųŲŽ┬Ż¼┤aą“┴ąÖz£yŲ„ī”▌ö╚ļą┼╠¢ųąĄ─“1”┤aŻ©═¼ŽÓ╝░Ę┤ŽÓ┤aŻ®▀MąąÖz£y▓ó▌ö│÷ĮŌš{öĄūųą“┴ąĪŻĮŌš{─ŻēKųąĄ─ŅAĘųŅlŲ„║═“1”┤aĘųŅlŲ„║═į┌░ļļp╣ż═©ą┼ĘĮ╩Įųą┐╔┼cš{ųŲ─ŻēK║Žė├ęį£p╔┘─┐ś╦Ų„╝■Ų¼╔Ž┘Yį┤Ą─š╝ė├ĪŻ

MSK š{ųŲ/ĮŌš{Ų„Ą─FPGA ─ŻēKųąŻ¼ėŗöĄŲ„ĪóĘųŅlŲ„║═ČÓ┬Ę▀xō±Ų„ė├VHDL │╠ą“┐╔ęį║åå╬īŹ¼FŻ¼┤aį¬ą“┴ąÖz£yŲ„Ą─▓┐ĘųVHDL ĮYśŗ├Ķ╩÷╚ńŽ┬Ż║

architecture behav of codesdect is

signal m : integer range 0 to 3;

signal sdata : std_logic_vector(2 downto 0);

begin

cdata<= wavenum;

process(clk,clr)

begin

if clr='1' then m<=0;

elsif clk'event and clk='1' then

case m is

when 0 => if datain = cdata (2) then m<=1; else m <= 0 ; end if;

…

when 2 => if datain = cdata (0) then m<=3; else m <= 0 ; end if;

when others => m <= 0;

end case;

end if;

end process;

process(m)

begin

if m=3 then outputt<='1';

else outputt<='0';

end if;

end process;

end behav;

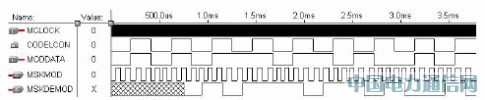

öĄūųMSK š{ųŲ/ĮŌš{Ų„─ŻēKį┌Altera ╣½╦ŠFPGAŻ║EP2C15AF256C8N ╔ŽīŹ¼FĪŻEP2C15 ╩ŪAltera ╣½╦Š╗∙ė┌90nm ╣ż╦ćĄ─Ą┌Č■┤·Cyclone Ų„╝■Ż©Cycloneó“Ż®Ż¼Ų¼ā╚╝»│╔14Ż¼448 ▀ē▌ŗå╬į¬Ż©LEŻ®Ż¼240Kb ŪČ╚ļ╩ĮRAM ēKŻ¼26 éĆ18×18 │╦Ę©Ų„Ż¼4 éƵiŽÓŁhŻ©PLLŻ®Ż¼Š▀ėąĖ▀╦┘▓ŅĘųI/O─▄┴”Ż¼į┌ę¶ęĢŅlČÓ├Į¾wĪóŲ¹▄ćļŖūėĪó═©ą┼╝░╣żśI┐žųŲŅIė“Ą╚ėąÅVĘ║Ą─▀mė├ąįŻ¼╩Ūę╗┐ŅĖ▀ąį─▄Ą═│╔▒ŠŲ„╝■ĪŻłD3 ╩ŪMSK š{ųŲ/ĮėĮŌš{Ų„Ą─Ģrą“Ę┬šµĮY╣¹ĪŻ

łD3 MSK š{ųŲ/ĮŌš{Ų„Ģrą“Ę┬šµ

ė╔łDųą┐╔ęŖŻ¼öĄūų╗∙Ħš{ųŲą┼╠¢MODDATA Įø▀^MSK š{ųŲŲ„▒╗š{ųŲĄĮĖ▀ŅlöĄūų▌d▓©╔ŽŻ¼ą╬│╔MSK ęčš{ą┼╠¢MSKMODŻ¼Ųõųą“0”┤a×ķ2.5 éĆ▌d▓©ų▄Ų┌Ż¼“1”┤a×ķ2 éĆ▌d▓©ų▄Ų┌Ż¼š{ųŲųĖöĄ×ķ0.5Ż¼═¼Ģr▌d▓©ŽÓ╬╗▀B└mĪŻMSKDEMOD ×ķĮė╩šČ╦MSK ĮŌš{║¾Ą─ą┼╠¢Ż¼│²┴╦é„▌öĢrčėŻ¼ĮŌš{ą┼╠¢═Ļ╚½╗ųÅ═┴╦░l╦═Č╦öĄūų╗∙Ħš{ųŲą┼╠¢ĪŻ

3 ĮYšō

MSK š{ųŲŠ▀ėą▌d▓©ŽÓ╬╗▀B└mŻ¼ŅlĦ└¹ė├┬╩Ė▀Ą─ā׳cŻ¼į┌═©│ŻĄ─æ¬ė├ųąąĶę¬īŻė├╝»│╔ļŖ┬Ęśŗ│╔š{ųŲ/ĮŌš{ļŖ┬ĘĪŻ╗∙ė┌ė▓╝■├Ķ╩÷šZčįė├FPGA īŹ¼FMSK š{ųŲ/ĮŌš{Ų„Ż¼┐╔│õĘų└¹ė├FPGAŲ¼ā╚┘Yį┤Ż¼╩╣öĄō■▓╔╝»£y┴┐┐žųŲ┼cé„▌ö╝»ųąė┌å╬ę╗ąŠŲ¼Ż¼ėą└¹ė┌╠ßĖ▀ŽĄĮyĄ─ĮøØ·ąį║═┐╔┐┐ąįŻ¼Š▀ėąę╗Č©Ą─æ¬ė├ārųĄĪŻ▒Š╬─ū„š▀äōą┬³cį┌ė┌╠ß│÷┴╦ę╗ĘN▒ŻūCš{ųŲųĖöĄ×ķ0.5 ═¼Ģr▌d▓©ŽÓ╬╗▀B└mĄ─öĄūųMSK ą┼╠¢Ą─įOėŗĘĮĘ©Ż¼ė├VHDL šZčįįOėŗ┴╦š{ųŲ/ĮŌš{─ŻēK▓óį┌FPGA Ų„╝■╔ŽīŹ¼FĪŻ